# High Efficiency 2.7A Synchronous Boost Convertor

### **General Description**

The LP6252 is a Synchronous current mode boost DC-DC converter. Its PWM circuitry with built-in 2.7A Current power MOSFET makes this converter highly power efficiently. Selectable high switching frequency allows faster loop response and easy filtering with a low noise output. The non-inverting input its error amplifier is connected to an internal 800mV precision reference voltage. Current mode control and external compensation network make it easy and flexible to stabilize the system.

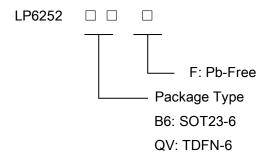

# **Ordering Information**

#### **Features**

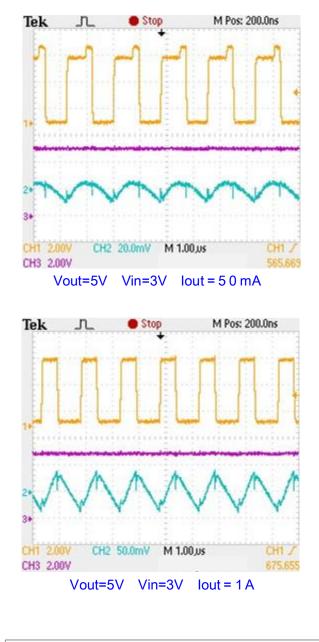

- ♦ Up to 95% efficiency

- Output to Input Disconnect at Shutdown Mode

- Shut-down current:<1uA

- Output voltage Up to 5.5V

- Over Output Voltage Protection

- Over Current Protection

- Over Temperature Protection

- Internal Compensation of Soft-start

- ♦ 550KHz fixed frequency switching

- High switch on current:2.7A

- Available in SOT23-6 and TDFN-6 Package

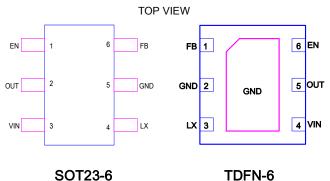

### **Pin Configurations**

# **Applications**

- ♦ Battery products

- ♦ Host OTG

♦ Audio power

### **Marking Information**

| Device           | Marking        | Package         | Shipping       |

|------------------|----------------|-----------------|----------------|

| LP6252B6F        | LPS            | SOT23-6         | 3K/REEL        |

|                  | 5VYWX          |                 |                |

| LP6252QVF        | LPS            | TDFN-6          |                |

|                  | 5TYW           |                 |                |

| Marking indicati | on:            |                 |                |

| Y:Production ye  | ar W:Productio | on period X:Pro | oduction batch |

ower LowPowerSemi 微源半導體

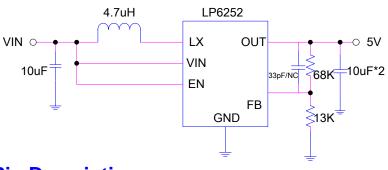

## **Typical Application Circuit**

## **Functional Pin Description**

| SOT23-6 | TDFN-6 | PIN Name | Description                                                      |

|---------|--------|----------|------------------------------------------------------------------|

|         |        |          | Regulation Feedback Input. Connect to an external resistive      |

| 6       | 1      | FB       | voltage divider from the output to FB to set the output voltage. |

|         |        |          | The pin is 0.8V.                                                 |

| 5       | 2      | GND      | Ground Pin.                                                      |

| 4       | 3      | LX       | Pin for switching.                                               |

| 3       | 4      | VIN      | Voltage supply input pin.                                        |

| 2       | 5      | OUT      | Voltage output Pin.                                              |

| 4       | 6      |          | Chip enable pin. LP6252 will turn on when EN=high, and turn off  |

| 1       | 6      | EN       | when EN=0.                                                       |

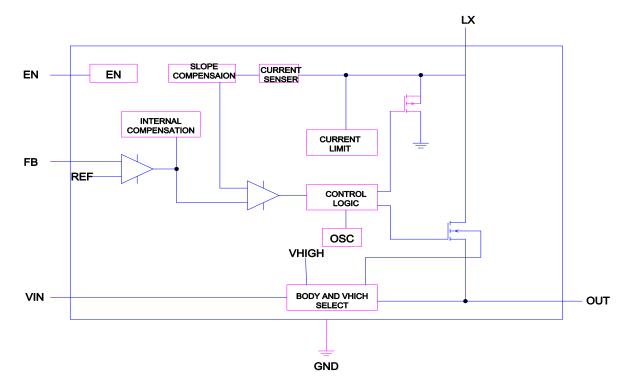

### **Function Block Diagram**

# **Absolute Maximum Ratings**

| Supply Input Voltage                  | 6V             |

|---------------------------------------|----------------|

| Power Dissipation, PD @ TA = 25°C     |                |

| Package Thermal Resistance            |                |

| SOT23-6, JA                           | 250°C/W        |

| TDFN-6, θja                           | 95°C/W         |

| Lead Temperature (Soldering, 10 sec.) | 260°C          |

| Recommended Operating Conditions      |                |

| Supply Input Voltage                  | 2.2V to 5.5V   |

| EN Input Voltage                      | 0V to 5.5V     |

| Operation Junction Temperature Range  | −40°C to 125°C |

| Operation Ambient Temperature Range   | −40°C to 85°C  |

### **Electrical Characteristics**

(Vin=3.5V,Vout=5V,Cin=10uF,Cout=22uF,L=4.7uH,R1=52.5K,R2=10K)

| Parameter                         | Conditions    |     | LP6252 |     |           |

|-----------------------------------|---------------|-----|--------|-----|-----------|

|                                   |               | Min | Тур    | Max | Units     |

| Supply Voltage                    |               | 2.2 |        | 5.5 | V         |

| Output Voltage Range              |               | 2.5 |        | 5.5 | V         |

| UVLO                              |               | 1.4 |        | 2.0 | V         |

| Over Output Voltage<br>Protection |               | 5.4 |        | 6   | V         |

| Supply Current(Shutdown)          | VEN=0V,Vin=5V |     | 0.05   | 1   | uA        |

| Feedback Voltage                  |               | 784 | 800    | 816 | mV        |

| Feedback Input Current            | VFB=0.8V      |     | 50     |     | nA        |

| Switching Frequency               |               |     | 550    |     | KHz       |

| Maximum Duty Cycle                |               | 80  | 90     | 95  | %         |

| EN Input Low Voltage              |               |     |        | 0.4 | V         |

| EN Input High Voltage             |               | 1.4 |        |     | V         |

| Low-side Current Limit            |               | 2.7 | 3      |     | А         |

| High-side On Resistance           | Vout=3.3V     |     | 110    |     | mΩ        |

| Low-side On Resistance            |               |     | 70     |     | $m\Omega$ |

# **Preliminary Datasheet**

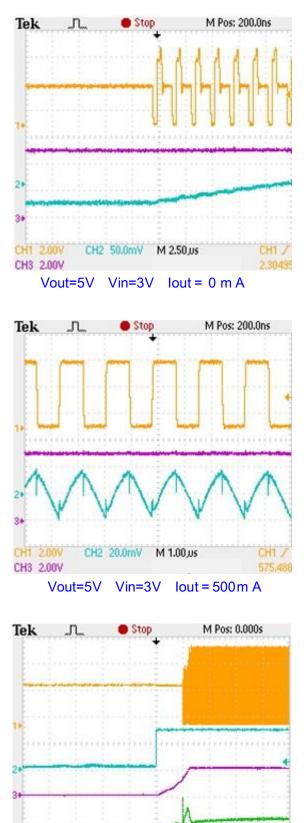

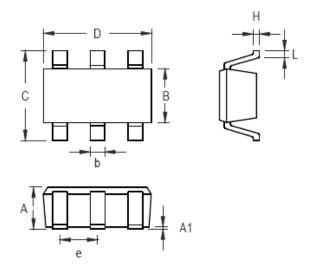

# **Typical Operating Characteristics**

CH2 2.00V

CH3 5.00V

CH4 500mA

M 1.00ms

**EN VS Vout**

CH2 .

<10Hz

#### **Operation Information**

The LP6252 uses a synchronous 550KHz fixed frequency, current-mode regulation architecture to regulate the output voltage. The LP6252 measures the output voltage through an external resistive voltage divider and compares that to the internal 0.8V reference to generate the error voltage to the inductor current to regulate the output voltage. The use of current-mode regulation improves transient response and control loop stability.

When the LP6252 is disable (EN=Low), both power switches are off. There is no current path from SW to OUT. Therefore, the output voltage discharges to ground. When the LP6252 is enabled(EN=High),a limited start-current charges the output voltage rising to SW, then the part operates in force PWM mode for regulating the output voltage to the target value. At the beginning of each cycle, the N-channel MOSFET switch is turned on, forcing the inductor current to rise, The current at the source of the switch is internally measured and converted to a voltage by the current sense amplifier. That voltage is compared to the error voltage. When the inductor current rises sufficiently, the PWM comparator turns off the switch, forcing the inductor current to the output capacitor through the internal P-Channel MOSFET rectifier, which forces the inductor current to decrease. The peak inductor current is controlled by the error voltage. Thus the output voltage controls the inductor current to satisfy the lode.

Set the output voltage by selecting the resistive voltage divider ratio. The voltage divider drops the output voltage to the 0.8V feedback voltage. Use a 100K resistor for R2 of the voltage divider. Determine the high-side resistor R1 by the equation:

Vout=(R1/R2+1) x VFB

#### Pre-Boost Current and Short Circuit Protect

Initially output voltage is lower than battery voltage, and the LP6252 enters pre-boost phase. During pre-boost phase, the internal NMOSFET/PMOSFET is turned off/on and a constant current is provided from battery to output until the output voltage close to the battery voltage. The constant current is limited by internal controller. If the output short to ground, the LP6252 also limits the output current to avoid damage condition

#### **Inductor Selection**

For a better efficiency in high switching frequency converter, the inductor selection has to use a proper core material such as ferrite core to reduce the core loss and choose low ESR wire to reduce copper loss. The most important point is to prevent the core saturated when handling the maximum peak current. Using a shielded inductor can minimize radiated noise in sensitive applications. The maximum peak inductor current is the maximum input current plus the half of inductor ripple current. The calculated peak current has to be smaller than the current limitation in the electrical characteristics. A typical setting of the inductor ripple current is 20% to 40% of the maximum input current. If the selection is 40%, the maximum peak inductor current is

#### Setting the Output Voltage

ower LowPowerSemi 微源半導體

$$\begin{split} I_{\text{PEAK}} = I_{\text{IN}(\text{MAX})} + \frac{1}{2}I_{\text{RIPPLE}} = 1.2 \times I_{\text{IN}(\text{MAX})} \\ = 1.2 \times \left[\frac{I_{\text{OUT}(\text{MAX})} \times V_{\text{OUT}}}{\eta \times V_{\text{IN}(\text{MIN})}}\right] \end{split}$$

The minimum inductance value is derived from the following equation :

$$L = \frac{\eta \times V_{IN(MIN)}^{2} \times \left[V_{OUT} - V_{IN(MIN)}\right]}{0.4 \times I_{OUT(MAX)} \times V_{OUT}^{2} \times f_{OSC}}$$

Depending on the application, the recommended inductor value is between  $2.2\mu$ H to  $4.7\mu$ H.

#### Input Capacitor Selection

For better input bypassing, low-ESR ceramic capacitors are recommended for performance. A 10µF input capacitor is sufficient for most applications. For a lower output power requirement application, this value can be decreased.

#### **Output Capacitor Selection**

For lower output voltage ripple, low-ESR ceramic capacitors are recommended. The tantalum capacitors can be used as well, but the ESR is bigger than ceramic capacitor. The output voltage ripple consists of two components: one is the pulsating output ripple current flows through the ESR, and the other is the capacitive ripple caused by charging and discharging.

$$V_{RIPPLE} = V_{RIPPLE\_ESR} + V_{RIPPLE\_C}$$

$$\cong I_{PEAK} \times R_{ESR} + \frac{I_{PEAK}}{C_{OUT}} \left( \frac{V_{OUT} - V_{IN}}{V_{OUT} \times f_{OSC}} \right)$$

#### **Layout Guide**

For high frequency switching power supplies, the PCB layout is important step in system application design. In order to let IC achieve good regulation, high efficiency and stability, it is strongly recommended the power components should be placed as close as possible. The set races should be wide and short. The feedback pin and then works of feedback and compensation should keep away from the power loops, and be shielded with a ground trace or plane to prevent noise coupling.

LP6252-00 Version 1.0 Aug.-2014 E-mail: marketing@lowpowersemi.com www.lowpowersemi.com Page 6 of 8

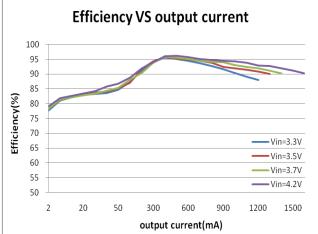

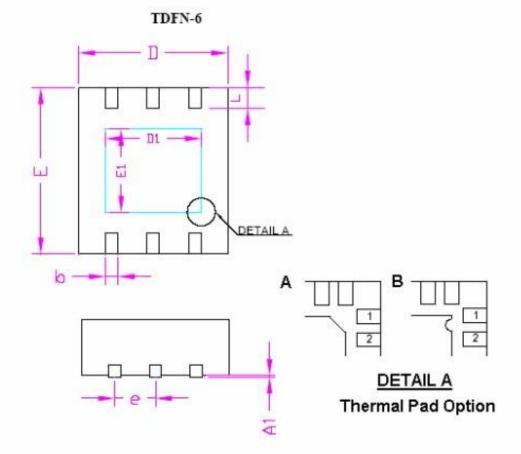

# **Packaging Information**

| Symbol | Dimensions | n Millimeters | Dimension | s In Inches |

|--------|------------|---------------|-----------|-------------|

| Symbol | Min        | Мах           | Min       | Max         |

| А      | 0.889      | 1.295         | 0.031     | 0.051       |

| A1     | 0.000      | 0.152         | 0.000     | 0.006       |

| В      | 1.397      | 1.803         | 0.055     | 0.071       |

| b      | 0.250      | 0.560         | 0.010     | 0.022       |

| С      | 2.591      | 2.997         | 0.102     | 0.118       |

| D      | 2.692      | 3.099         | 0.106     | 0.122       |

| е      | 0.838      | 1.041         | 0.033     | 0.041       |

| Н      | 0.080      | 0.254         | 0.003     | 0.010       |

| L      | 0.300      | 0.610         | 0.012     | 0.024       |

SOT-23-6 Surface Mount Package

| SYMBOLS | MILLIMETERS |      | INCHES |       |

|---------|-------------|------|--------|-------|

|         | MIN.        | MAX. | MIN.   | MAX.  |

| A       | 0.70        | 0.80 | 0.028  | 0.031 |

| A1      | 0.00        | 0.05 | 0.000  | 0.002 |

| b       | 0.20        | 0.40 | 0.008  | 0.016 |

| D       | 1.90        | 2.10 | 0.075  | 0.083 |

| D1      | 1.40        |      | 0.055  |       |

| E       | 1.90        | 2.10 | 0.075  | 0.083 |

| E1      | 0.80        |      | 0.031  |       |

| e       | 0.65        |      | 0.026  |       |

| L       | 0.25        | 0.45 | 0.010  | 0.018 |