### PROGRAMMABLE PERIPHERAL INTERFACE

#### TMP8255AP-5

### GENERAL DESCRIPTION AND FEATURES

The TMP8255A (hereinafter referred to as PPI) is a high Speed programmable input/output interface with three 8-bit I/O ports. 24 I/O ports are divided into two groups (Port A and Port B) which are programmable independently by control words provided by MPU. The PPI has three operation modes (Mode 0, 1 and 2) and is capable of versatile interface between MPU and peripheral devices.

- (1)  $5V \pm 5\%$  Single power supply

- (2) 24 programmable I/O ports

- (3) Three operation modes (Mode 0, Mode 1, Mode 2)

- (4) Bit set/reset capability

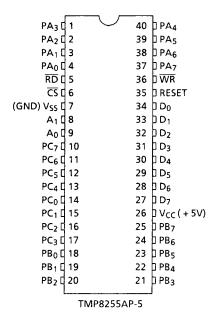

# 2. PIN CONNECTIONS (TOP VIEW)

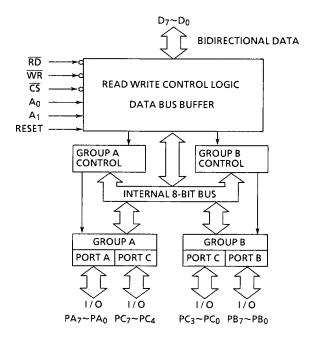

# 3. BLOCK DIAGRAM

# 4. PIN NAMES AND PIN FUNCTIONS

| Pin Name                         | Number<br>of Pin | Input/Output<br>3-state | Function                                                                                                                                                                                                                                                                                                                |

|----------------------------------|------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D <sub>0</sub> ~D <sub>7</sub>   | 8                | I/O<br>3-STATE          | 3-state bidirectional 8-bit data bus. Used for data transfer with MPU. Also, used for transfer of control words to PPI and status information from PPI.                                                                                                                                                                 |

| PA <sub>7</sub> ~PA <sub>0</sub> | 8                | I/O<br>3-STATE          | 3-state 8-bit I/O Port A.  Operation mode and input/output configuration are defined by software. Port A contains the output latch buffer and input latch.                                                                                                                                                              |

| PB <sub>7</sub> ~PB <sub>0</sub> | 8                | I/O<br>3-STATE          | 3-state 8-bit I/O Port B.  Operation mode and input/output configuration are defined by software. Port B contains the output latch buffer and input latch.                                                                                                                                                              |

| PC <sub>7</sub> ~PC <sub>0</sub> | 8                | I/O<br>3-STATE          | 3-state 8-bit I/O Port C. Operation mode and input/output configuration are defined by software. Port C can be divided into two 4-bit ports by the mode control and also, used as the control signal for Port A and Port B. In this case, 3 bits of PC0 to PC2 are used for Port B and 5 bits of PC3 to PC7 for Port A. |

| <u>cs</u>                        | 1                | Input                   | Chip select input. When this terminal is at "L" level, data transfer PPI and MPU becomes possible. At "H" level, the data bus is placed in the high impedance state and control from the processor is ignored.                                                                                                          |

| RD                               | 1                | Input                   | Read signal.  When this terminal is at "L" level, data that is input into the port is transferred to MPU.                                                                                                                                                                                                               |

| WR                               | 1                | Input                   | Write signal. When this terminal is at "L" level, data or control word is written into PPI from MPU.                                                                                                                                                                                                                    |

| A <sub>0</sub> , A <sub>1</sub>  | 2                | Input                   | Used for selecting Port A, B, C and the control registers. Nurmally, this terminal is connected to low order 2 bits of the address bus.                                                                                                                                                                                 |

| RESET                            | 1                | Input                   | When this terminal is at "H" level, all internal registers including the control register are cleared. In addition, all ports (Port A, B, C) are placed in the input mode (high impedance) of mode 0.                                                                                                                   |

| Vcc                              | 1                | Power<br>Supply         | 5V                                                                                                                                                                                                                                                                                                                      |

| V <sub>SS</sub>                  | 1                | Power<br>Supply         | GND                                                                                                                                                                                                                                                                                                                     |

## 5. FUNCTIONAL DESCRIPTION

The PPI is a programmable peripheral interface with three 8-bit ports (Port A, B and C) and two control registers. 24 I/O ports are divided into 12-bit group A and group B. Group A consists of Port A and high order 4 bits of Port C, while Group B consists of Port B and low order 4 bits of Port C. Each group is independently programmable by control words provided from MPU. There are three operation modes available for the PPI. In mode 0, two 8-bit I/O ports and two 4-bit I/O ports can be programmed as input or output ports, respectively. In mode 1, 24 I/O ports are divided into Group A and Group B. 8 bits of each group are used as input or output port and of the remaining 4 bits, 3 bits are used as handshaking and interrupt control signal. Mode 2 is applicable only to group A and the ports are used as a bidirectional 8-bit data bus and 5-bit control signal. In case of Port C being used as the output, any bits of Port C can be set/reset.

There are two control registers; one is used for mode setting and the other for bit set/reset control. The control registers can only be written into. Further, when the reset input (RESET) becomes "1", the control registers are reset and all I/O ports are placed in input mode (high impedance status).

| A <sub>1</sub> | A <sub>0</sub> | CS | RD | WR | Function                    |  |  |  |  |  |  |

|----------------|----------------|----|----|----|-----------------------------|--|--|--|--|--|--|

| 0              | 0              | 0  | 0  | 1  | Data bus ← Port A           |  |  |  |  |  |  |

| 0              | 1              | 0  | 0  | 1  | Data bus ← Port B           |  |  |  |  |  |  |

| 1              | 0              | 0  | 0  | 1  | Data bus ← Port C           |  |  |  |  |  |  |

| 0              | 0              | 0  | 1  | 0  | Port A ← Data bus           |  |  |  |  |  |  |

| 0              | 1              | 0  | 1  | 0  | Port B ← Data bus           |  |  |  |  |  |  |

| 1              | 0              | 0  | 1  | 0  | Port C ← Data bus           |  |  |  |  |  |  |

| 1              | 1              | 0  | 1  | 0  | Control register ← Data bus |  |  |  |  |  |  |

| ×              | ×              | 1  | ×  | ×  | Data bus ≈ 3-state          |  |  |  |  |  |  |

| ×              | ×              | 0  | 1  | 1  | Data bus                    |  |  |  |  |  |  |

| 1              | 1              | 0  | 0  | 1  | inhibition of combination   |  |  |  |  |  |  |

Table 5.1 Basic Operation of TMP8255A

#### 5.1 MODE SELECTION

There are three basic modes of operation that can be selected by control words.

Mode 0-Basic I/O (Group A, Group B)

Mode 1-Strobe input/Strobe output (Group A, Group B)

Mode 2-Two-way bus (Port A only)

Operation modes for Group A and Group B can be independently defined by the control word from the MPU. If  $D_7$  is set to "1" in writing a control word into the PPI, on operation mode is selected, while of  $D_7 = "0"$ , the set/reset function for Port C is selected.

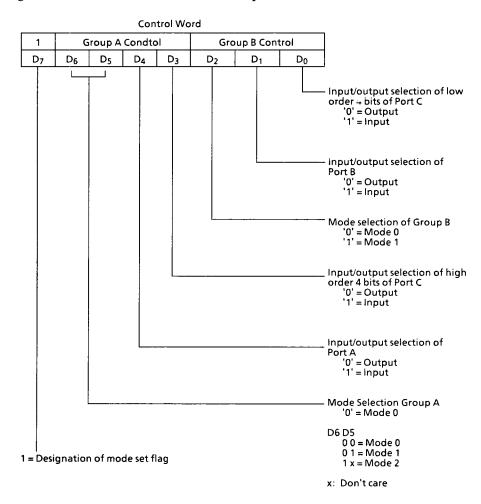

#### 5.1.1 Control word to define operation mode

Figure 5.1 shows the control words to define operation mode of the TMP8255A.

Figure 5.1 Control Word for Mode Selection

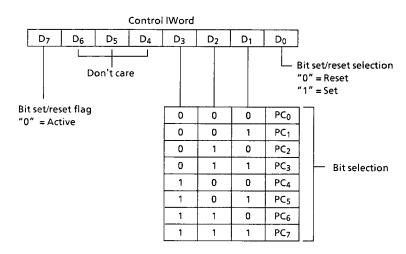

#### 5.1.2 Port C bit set/reset control word

Any bit of 8 bits of Port C can be set/reset by Port C bit set/reset control word. Figure 5.2 shows the Port C bit set/reset control word.

Figure 5.2 Control Word for Bit Set/Reset

### 5.2 OPERATION MODES

#### 5.2.1 Mode 0 (Basic I/O)

This functional configuration is used for simple input or output operations. No 'handshaking' is required and data is simply written to or read from a specified part. Output data to the ports from MPU are latched out but input data from the ports are not latched.

In Mode 0, 24 I/O ports are divided into four groups of Port A (8 BITS), Port B (8 bits), high order 4 bits of Port C and low order 4 bits of Port C. Each port can be programmed to be input or output. The configuration of each port are determined according to the contents of Bit 4 (D<sub>4</sub>), 3 (D<sub>3</sub>), 1 (D<sub>1</sub>) and 0 (D<sub>0</sub>) of the control word for mode selection.

The I/O configuration of each port in Mode 0 are shown in Table 5.2.

| No             | de Setting     | Control W      | ord            | Port A | Port C                              | D = w4 D | Port C                              |  |

|----------------|----------------|----------------|----------------|--------|-------------------------------------|----------|-------------------------------------|--|

| D <sub>4</sub> | D <sub>3</sub> | D <sub>1</sub> | D <sub>0</sub> | Port A | (PC <sub>7</sub> ~PC <sub>4</sub> ) | Port B   | (PC <sub>3</sub> ~PC <sub>0</sub> ) |  |

| 0              | 0              | 0              | 0              | Out    | Out                                 | Out      | Out                                 |  |

| 0              | 0              | 0              | 1              | Out    | Out                                 | Out      | l In                                |  |

| 0              | 0              | 1              | 0              | Out    | Out                                 | ln       | Out                                 |  |

| 0              | 0              | 1              | 1              | Out    | Out                                 | In       | ln                                  |  |

| 0              | 1              | 0              | 0              | Out    | In                                  | Out      | Out                                 |  |

| 0              | 1              | 0              | 1              | Out    | in                                  | Out      | In                                  |  |

| 0              | 1              | 1              | 0              | Out    | In                                  | In       | Out                                 |  |

| 0              | 1              | 1              | 1              | Out    | In                                  | In       | in                                  |  |

| 1              | 0              | 0              | 0              | In     | Out                                 | Out      | Out                                 |  |

| 1              | 0              | 0              | 1              | In     | Out                                 | Out      | In                                  |  |

| 1              | 0              | 1              | 0              | In     | Out                                 | In       | Out                                 |  |

| 1              | 0              | 1              | 1              | In     | Out                                 | In       | in                                  |  |

| 1              | 1              | 0              | 0              | In     | in                                  | Out      | Out                                 |  |

| 1              | 1              | 0              | 1              | In     | in                                  | Out      | ln                                  |  |

| 1              | 1              | 1              | 0              | In     | in                                  | In       | Out                                 |  |

| 1              | 1              | 1              | 1              | In     | In                                  | In       | In                                  |  |

Figure 5.3 Port definition in Mode 0

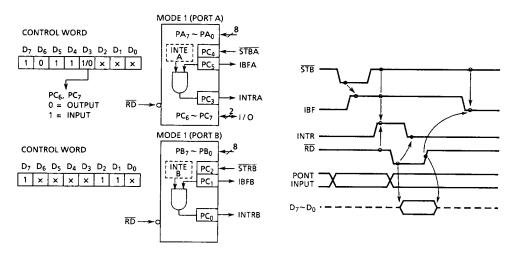

#### 5.2.2 Mode 1 (Strobe I/O)

In Mode 1, input/output of port data is performed in conjunction with the strobe signals or 'handshaking' signals. Port C is used to control Port A or Port B.

The basic operatings in Mode 1 are as follows:

- Mode 1 can be set for two groups of Group A and Group B.

- Each group consist of 8-bit data port and 4-bit control/data port.

- The 8-bit data port can be set as input or output port.

- The control/data port is used as control or status of the 8-bit data port.

# (1) When used as the input port in Mode 1:

• STB (Strobe Input)

At "0", input data is loaded in the internal input latch in the port.

In this case, a control signal from MPU is not concerned and data is input from the port any time. This data is not read out on the data bus unless MPU executes an input instruction.

• IBF (Input Buffer Full F/F Output)

When data is loaded in the internal input latch from the port, this output is set to "1". IBF is set ("1") by  $\overline{STB}$  input being reset and is reset ("0") by the rising edge of  $\overline{RD}$  input.

INTR (Interrupt Request Output)

Used for the interrupt process of data loaded in the internal input latch. When  $\overline{STB}$  input is at "0" if INTE (INTE flag) in the PPI is in the enabled state ("1"), IBF is set to "1". INTR is set to "1" immediately after the rising edge of this  $\overline{STB}$  input and reset to "0" by the falling edge of  $\overline{RD}$  input.

The INTE flags of Group A and Group B are controlled as follows:

INTEA-Control by bit set/reset of PC4

INTEB-Control by bit set/reset of PC2

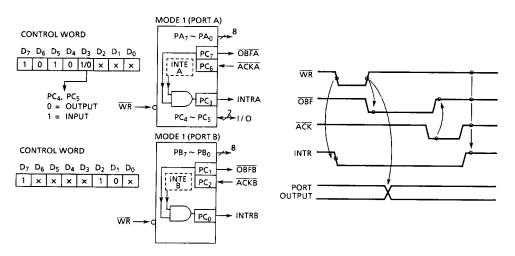

- (2) When used as the output port in Mode 1:

- OBF (Output Buffer Full F/F Output)

This is a flag which shows that MPU has written data into a specified port.  $\overline{OBF}$  is set to becomes "0" at the rising edge of  $\overline{WR}$  signal and is set to "1" at the falling edge of  $\overline{ACK}$  (Acknowledge input) signal.

• ACK (Acknowledge Input)

ACK signal is sent to the PP1 as a response from a peripheral device that received data from the port.

• INTR (Interrupt Request Output)

When a peripheral device received data from MPU, INTR is set to "1" and the interrupt is requested to MPU. If  $\overline{ACK}$  signal is received when INTE flag is in the enable state,  $\overline{OBF}$  is set to "1" and INTR signal becomes "1" immediately after the rising edge of  $\overline{ACK}$  signal. Further, INTR is reset at the falling edge of  $\overline{WR}$  signal when data is written into the PPI by MPU.

The INTE flags of Group A and Group B are controlled as follows:

INTEA-Control by bit set/reset of PC6

INTEB-Control by bit set/reset of PC2

Figure 5.4 Example of Strobe Input in Mode 1

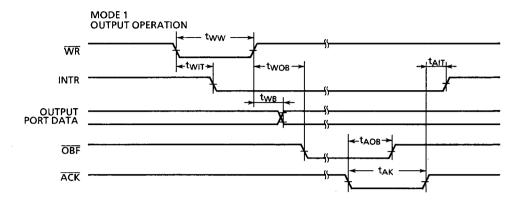

Figure 5.5 Example of Strobe Output in Mode 1

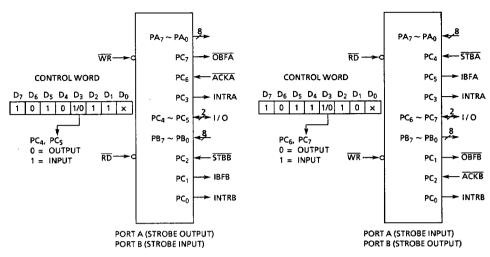

Figure 5.6 Example of Port A output, Port B Input in Mode 1

Figure 5.7 Example of Port A Input, Port B Output in Mode 1

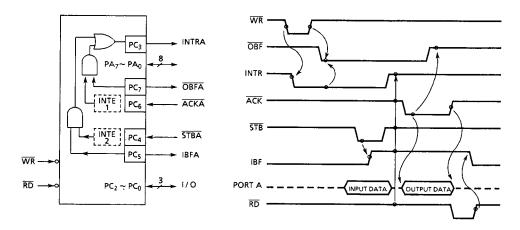

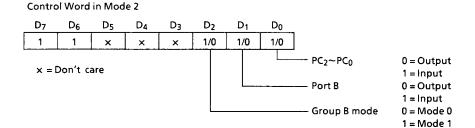

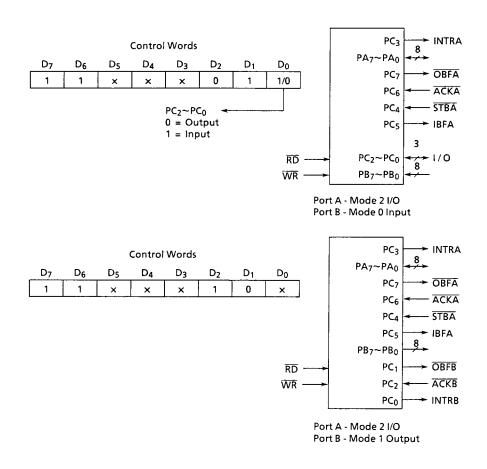

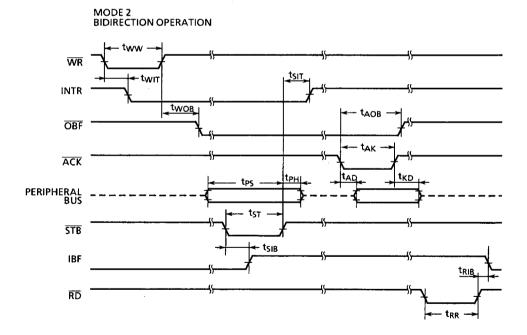

#### 5.2.3 Mode 2 (Strobed Bidirectional Bus I/O)

In this mode, Port A is used as 8 bits bidirectional bus for data transfer with a peripheral device. This mode is applicable only to Group A, which consists of an 8-bit bidirectional bus (Port A 8-bit) and 5-bit control signals (high order 5 bits of Port C). The bidirectional bus (Port A) has both the internal input and output registers. When group A is set in Mode 2, Group B can be set independently. These are 5 control signals as follows when Group A is used in Mode 2.

#### OBF (Output buffer Full F/F Output)

When MPU writes data into of Port A,  $\overline{OBF}$  is set to "0" to inform a peripheral device that the PPI is ready to output data. However, Port A is dept in the floating (high impedance) state until  $\overline{ACK}$  input signal is received.

### • ACK (Acknowledge Input)

When  $\overline{ACK}$  signal is set to "0", the data of the 3-state output buffer of Port A is send out. If  $\overline{ACK}$  signal is at "1", Port A is in the high impedance state.

### • STB (Strobe Input)

When  $\overline{STB}$  input is set to "0", the data from peripheral devices are held in the input latch. When the active  $\overline{RD}$  signal is input into the PPI, the latched input data are output on the system data bus  $(D_7-D_0)$ .

• IBF (Input Buffer Full F/F Output)

When data from peripheral devices are held in the input latch, IBF is set to "1".

• INTR (Interrupt Request Output)

INTR is the output to request the interrupt to MPU and its function is the same as that in Mode 1. There are two interrupt enable flip-flop (INTE), INTE1 corresponds to INTEA in Mode 1 output and INTE2 to INTEA in Mode 1 input.

INTE 1-Used to generate INTR signal in conjunction with  $\overline{OBF}$  and  $\overline{ACK}$  signals, and is controlled by PC6 bit set/reset.

INTE 2-Used to generate INTR signal in conjunction with IBF and STB signals, and is controlled by PC<sub>4</sub> bit set/reset.

Figure 5.8 shows the operating example and the timing diagram in Mode 2.

Figure 5.8 Operating example in Mode 2

Figure 5.9 Control Word and Configuration in Mode 2

Figure 5.10 Example in Combination with Mode 2 and Other Mode

### 5.2.4 Pecautions for use in Mode 1 and 2

When used in Mode 1 and 2, bits which are not used as control or status in Port C can be used as follows.

If programmed as the input, they are accessed by normal Port C read.

If Programmed as the output, high order bits of Port C (PC7-PC4) are accessed using the bit set/reset function. As to low order bits of Port C (PC3-PC0), in additions ot access by the bit set/reset function, 3 bits only can be accessed by normal writing.

## 5.3 READING PORT C STATUS

When Port C is used as the control port, that is, when Port C is used in Mode 1 or Mode 2, the status information of the control word can be read out by a normal read operation of Port C.

Table 5.2 Status Word Format of Port C

| Data Mode     | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub>  | D <sub>1</sub> | D <sub>0</sub> |

|---------------|----------------|----------------|----------------|----------------|----------------|-----------------|----------------|----------------|

| Mode 1 Input  | 1/0            | 1/0            | IBFA           | INTEA          | INTRA          | INTEB           | IBFB           | INTRB          |

| Mode 1 Output | OBFA           | INTEA          | 1/0            | 1/0            | INTRA          | INTEB           | OBFB           | INTRB          |

| Mode 2        | OBFA           | INTE1          | IBFA           | INTE2          | INTRA          | By Group B Mode |                | ode            |

# 6. ELECTRICAL CHARACTERISTICS

# 6.1 ABSOLUTE MAXIMUM RATINGS

| Symbol           | ltem                          | Rating                      | Unit |

|------------------|-------------------------------|-----------------------------|------|

| V <sub>CC</sub>  | Supply Voltage                | - 0.5 to 7.0                | ٧    |

| VIN              | Input Voltage                 | -0.5to V <sub>CC</sub> +7.0 | V    |

| PD               | Power Dissipation             | 1                           | w    |

| TSOLDER          | Soldering Temperature (10sec) | 260                         | င    |

| T <sub>STG</sub> | Strobe Temperature            | - 65 to + 150               | င    |

| TOPR             | Operating Temperature         | 0 to +70                    | °    |

### 6.2 DC ELECTRICAL CHARACTERISTICS

TA = 0°C to 70°C,  $V_{CC} = 5V \pm 5\%$ ,  $V_{SS} = 0V$

| SYMBOL          | ITEM                                        |               | TEST CONDITION                                       | MIN.       | TYP.         | MAX.         | UNIT |

|-----------------|---------------------------------------------|---------------|------------------------------------------------------|------------|--------------|--------------|------|

| VIL             | Input Low Voltage                           |               |                                                      | -0.5       | _            | 0.8          | ٧    |

| V <sub>IH</sub> | Input High Voltage                          |               |                                                      | 2.2        | _            | Vcc          | ٧    |

| V <sub>OL</sub> | Output Low Voltage                          | (DB)<br>(PER) | I <sub>OL</sub> = 2.5mA<br>I <sub>OL</sub> = 1.7mA   | _<br>_     | <del>-</del> | 0.45<br>0.45 | > >  |

| V <sub>OH</sub> | Output High Voltage                         | (DB)<br>(PER) | i <sub>OH</sub> = -400μA<br>i <sub>OH</sub> = -200μA | 2.4<br>2.4 | -            | -            | > >  |

| I <sub>IL</sub> | Input Leak Current                          |               | 0 ≨ V <sub>IN</sub> ≦ V <sub>CC</sub>                | _          | -            | ± 10         | μА   |

| lofL            | Output Leak Current<br>(High Impedance Stat | e)            | 0 ≤ V <sub>OUT</sub> ≤ V <sub>CC</sub>               | -          | _            | ± 10         | μА   |

| (Note 1)        | Darlington Drive Curre                      | nt            | V <sub>EXT</sub> = 1.5V<br>R <sub>EXT</sub> = 750Ω   | - 1.0      | _            | - 4.0        | mA   |

| lcc             | Operating Supply Curr                       | ent           | I/O cycle Time 1<br>usec                             | -          | -            | 120          | mA   |

Note: Applied for optional 8 I/O terminals in Port B and Port C.

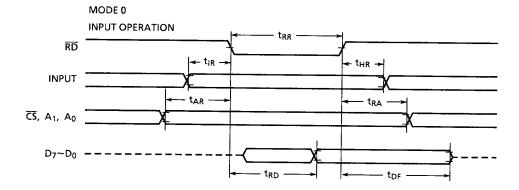

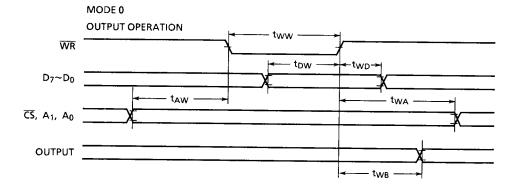

### 6.4 AC ELECTRICAL CHARACTREISTICS

TA = 0°C to 70°C, VCC =  $5V \pm 5\%$ , VSS = 0V

| SYMBOL           | DADAMETER                                                | TMP82 | 55AP-5 | UNIT |

|------------------|----------------------------------------------------------|-------|--------|------|

| STIVIBUL         | PARAMETER                                                | MIN.  | MAX.   | UNII |

| tar              | Address set-up time for RD fall                          | 0     | _      | ns   |

| t <sub>RA</sub>  | Address hold time for RD rise                            | 0     | _      | ns   |

| t <sub>RR</sub>  | RD pulse width                                           | 300   | -      | ns   |

| t <sub>RD</sub>  | Delay from RD fall to decided data output                | T -   | 200    | ns   |

| t <sub>DF</sub>  | Time from RD rise to data bus floating                   | 10    | 100    | ns   |

| t <sub>RV</sub>  | Time from RD or WR rise to next RD or WR fall            | 850   | _      | ns   |

| t <sub>AW</sub>  | Address set-up time for WR fall                          | 0     | _      | ns   |

| t <sub>WA</sub>  | Address holding time for WR rise                         | 20    | -      | ns   |

| t <sub>WW</sub>  | WR pulse width                                           | 300   | - "    | ns   |

| t <sub>DW</sub>  | Bus data set-up time for WR rise                         | 100   |        | ns   |

| t <sub>WD</sub>  | Bus data holding time for WR rise                        | 30    | -      | ns   |

| t <sub>WB</sub>  | Delay from WR rise to decided data output                | _     | 350    | ns   |

| t <sub>IR</sub>  | Port data set-up time for RD fall                        | 0     | _      | ns   |

| t <sub>HR</sub>  | Port data holding time for RD rise                       | 0     | _      | ns   |

| tak              | ACK pulse width                                          | 300   | _      | ns   |

| t <sub>ST</sub>  | STB pulse width                                          | 500   | -      | ns   |

| tps              | Port data set-up time for STB rise                       | 0     | -      | ns   |

| t <sub>РН</sub>  | Port data holding time for STB rise                      | 180   | -      | ns   |

| t <sub>AD</sub>  | Delay from ACK fall to decided data output               | _     | 300    | ns   |

| t <sub>KD</sub>  | Time from ACK rise up to port (Port A in Mode2) floating | 20    | 250    | ns   |

| t <sub>WOB</sub> | Delay from WR rise to OBF fall                           | _     | 650    | ns   |

| t <sub>AOB</sub> | Delay from ACK fall to OBF rise                          | _     | 350    | ns   |

| t <sub>SIB</sub> | Delay from STB fall to IBF rise                          | -     | 300    | ns   |

| t <sub>RIB</sub> | Delay from RD fall to IBF rise                           | _     | 300    | ns   |

| t <sub>RIT</sub> | Delay from RD fall to INTR fall                          | _     | 400    | ns   |

| t <sub>SIT</sub> | Delay from ACK rise to INTR rise                         | _     | 300    | ns   |

| t <sub>AIT</sub> | Delay from ACK rise to INTR rise                         | -     | 350    | ns   |

| twiT             | Delay from WR rise to INTR fall                          | _     | 450    | ns   |

Note: 1. When the power supply is turned ON, reset pulse duration must be active for at least 500 ns or more.

2. AC Measuring Point Input Voltage Output Voltage

$V_{IH} = 2.0V$ ,  $V_{IL} = 0.8V$  $V_{OH} = 2.0V$ ,  $V_{OL} = 0.8V$

CL=150pF.

# 6.4 CAPACITANCE

TA = 25°C,  $V_{CC} = V_{SS} = 0V$

| SYMBOL | ITEM              | TEST CONDITION        | MIN. | TYP. | MAX. | UNIT |

|--------|-------------------|-----------------------|------|------|------|------|

| CIN    | Input Capacitance | f <sub>C</sub> = 1MHz | -    |      | 10   | рF   |

| C1/0   | I/O Capacitance   | (*)                   | _    |      | 20   | pF   |

<sup>\*:</sup> All terminals except that to be measured should be earthed.

# 7. TIMING DIAGRAM

Figure 7.1 Timing diagram

Figure 7.2 Timing diagram

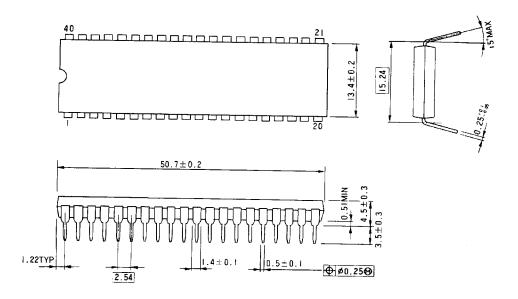

# 8. PACKAGE DIMENSION

# 8.1 PLASTIC PACKGE

DIP40-P-600

Unit: mm

Note: Each lead pitch is 2.54mm, and all the leads are located within  $\pm 0.25$ mm from their theoretical positions with respect to No.1 and No.40 leads.