## **Inverters form three-phase VCO**

Al Dutcher, AL Labs, West Deptford, NJ

OU SOMETIMES NEED an inexpensive VCO that can produce evenly spaced three-phase outputs over a wide frequency range. You could use tracking all-phase filters with only one oscillator, but this technique is difficult to implement and offers limited range. Other methods, such as using a DSP, are feasible, but they're complex and expensive. The inspiration for the VCO in Figure 1 came from Texas Instruments' application notes of years ago, detailing the use of unbuffered U-type inverters for use in ring oscillators. The application note's circuit consists of only the inverters. The circuit generates relatively squarish waveforms. Any ring oscillator's operation depends on the fact that an odd number of

inversions exists around the loop. Any odd number of inverters would work. The feedback is inverting, or negative. The

feedback creates an initial bias equilibrium at the transition voltage for the gates.

Loop gain greater than unity is a necessary condition for oscillation. Unbuffered inverters typically have a gain of 15 or thereabouts at dc and approximately 7 with capacitive loads. Three inverters thus have a total gain of more

than 340, which is plenty for oscillation. At high frequencies, the inverters exhibit a lagging phase shift arising from propagation delay. Enough lagging shift added to the inversions ultimately turns the total inversion into noninversion. The circuit of **Figure 1** starts out with the 180° inversion and adds 60° of lag for 240° per stage. Three stages of 240° works out to 720° total. This figure represents two complete trips around the phase circle for noninversion. Noninversion implies regeneration, which begets oscillation.

A ring-type oscillator generates 3-phase outputs over a wide frequency range.

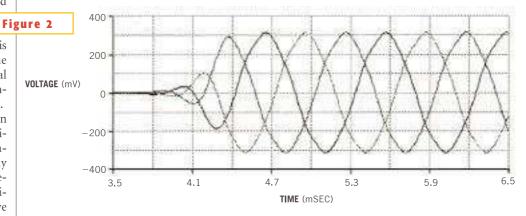

The circuit in Figure 1 generates 120°-spaced, 600-mV p-p outputs.

With no added capacitors, the circuit of **Figure 1** can operate at frequencies as high as tens of megahertz using 74ACU04 gates. Added capacitors can drop the frequency to usable levels. The frequency equates to  $I_{\rm DD}/3C$ . For lower frequency applications, 74HCU04 gates are suitable, because they're less sensitive to layout considerations.

The diodes in **Figure 1** perform two tasks. First, they limit the excursions of the gates to 600 mV p-p, so that the gates always operate in their linear region. Sec-

ond, they allow the gates to operate as current diverters, alternately charging and discharging the capacitors. The rate at which the capacitors discharge depends on the common supply current to the inverters. This rate and, hence, the oscillation frequency is proportional to the operating current. The range of frequencies over which the circuit can operate is more than 1000-to-1 (supply current from 10  $\mu$ A to 10 mA). Note that at the low-current, low-frequency end of the range, the circuit cannot supply much

102 EDN | AUGUST 2, 2001 www.ednmag.com

## designideas

signal current and might need buffering.

Figure 2 shows the three-phase waveforms. The concept doesn't work well with normal ac- or HC-buffered gates, because they have far too much gain and would drive the nodes into square waves. The ACU and HCU types are somewhat obscure, but they nonetheless have multiple sources. Don't forget to ground the inputs of the remaining three gates of these hex devices. Floating inputs are verboten with all CMOS devices.

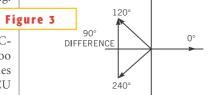

The circuit generates three equally spaced outputs. Because it generates substantially sinusoidal outputs, you can easily obtain quadrature-spaced outputs by trigonometric means (Figure 3). You can

Vector subtraction of two outputs produces a  $90^{\circ}$  quadrature signal.

connect a differential amplifier to the 120 and 240° outputs. It rejects the commonmode, 180° components. The difference between these two outputs is at 90°, and it tracks well over the range of the oscillator. You can use the same type of differential amplifier to amplify the 0° out-

put so that the amplifier delays track at higher frequencies. In principle, you can extract any set of phase angles by the judicious adjustment of component amplitudes in the external circuits. The circuit's main drawback is that it does not have a high-Q resonator attached, so phase noise could be a problem. When you incorporate the circuit into a relatively tight PLL circuit, the performance improves considerably. The capabilities of this oscillator allow it to lock over a wide range of frequencies.

Is this the best Design Idea in this issue? Vote at www.ednmag.com/edn mag/vote.asp.

## Power inverter is bidirectional

Tom Napier, North Wales, PA

F YOU WANT to swap charge in either direction between unevenly loaded positive and negative battery buses, you need an inverting dc transformer. One implementation is the symmetrical flyback converter shown in Figure 1. The circuit can generate a negative output from a positive supply or a positive output from a negative supply. When the circuit starts up, the substrate diode of the output FET bootstraps the output voltage to the point where synchronous switching takes over. When the gate-switching signal is symmetrical, the output voltage is approximately -95% of the input voltage, and the efficiency is greater than 80%. You can obtain voltage step-up or step-down by adjusting the switching ratio.

When I used the circuit between two 4V lead-acid batteries, a comparator adjusted the switch ratio to drive charge in the desired direction. The circuit automatically replaces charge drained from one battery to the other. In a short-battery-life application, the 2.5-mA standby current from each battery may be negligible. Using lower-gate-capacitance, FETs can reduce losses. Alternatively, you

47k Figure 1 RATIO ADJUST POSITIVE NEGATIVE INPUT/OUTPUT OUTPUT/INPUT 10k DISC RST †6.8 μF (CMOS) 6.8 μF OUT TRIG IRF520 IRF9530 1000 pF

An inverter circuit swaps charges between opposite-polarity batteries.

can add gates to the drive circuit to turn off both FETs whenever the battery voltages balance. The minimum input voltage is a function of the gate thresholds of the FETs. The  $\pm 9V$  rating of the CMOS 555 timer sets the maximum volt-

age. My prototype supplies approximately 100 mA.

Is this the best Design Idea in this issue? Vote at www.ednmag.com/edn mag/vote.asp.

104 EDN | AUGUST 2, 2001 www.ednmag.com