Loewe Opta GmbH Postfach 1554 96305 Kronach Industriestraße 11 96317 Kronach Tel: (09261) 99-0 Fax (09261) 9 54 11

e-mail: loewe@loewe.de http://www.loewe.de

231-90415.917

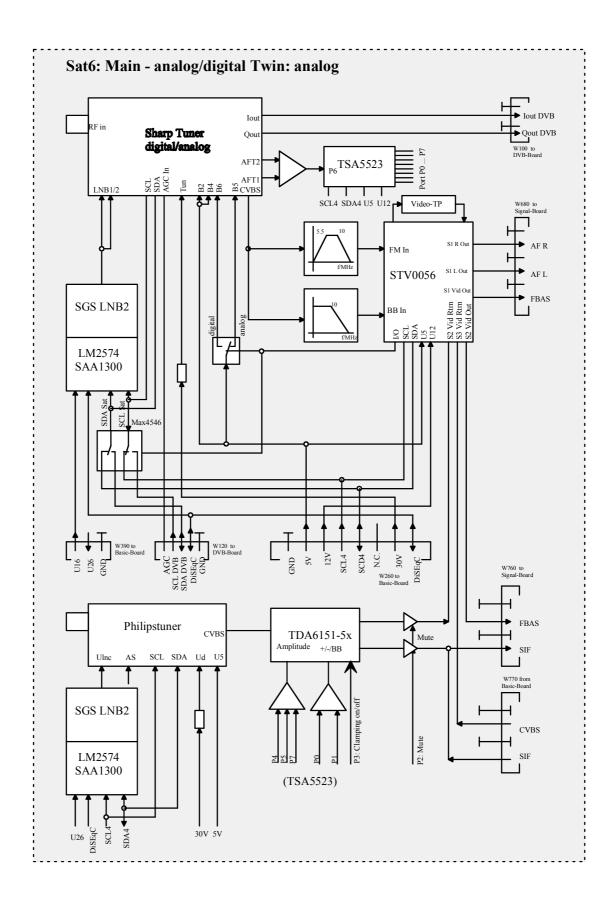

|                                            |    | 3.4 | .4  | DVB demodulation and fault correct        | tion |

|--------------------------------------------|----|-----|-----|-------------------------------------------|------|

| 1 Introduction                             |    |     | _   | 56                                        |      |

| 1.1 Foundations of 100 hz technology       |    | 3.4 |     | LNC supply                                |      |

| 1.1.1 Prerequisites for 100 Hz             |    |     |     | board                                     |      |

| 1.1.2 100 Hz display modes                 |    | 4.1 |     | vice control                              |      |

| 1.1.3 Mode AABB                            |    | 4.1 |     | The infrared sensor                       |      |

| 1.1.4 Mode ABAB                            | 9  | 4.1 |     | Infrared receiver                         |      |

| 1.1.5 Mode AA'B'B                          | 9  | 4.1 | .3  | The SDA 6000 central control unit.        |      |

| 1.1.6 Mode AA*BB*                          | 9  | 4.1 | .4  | Reset                                     |      |

| 2 Basic board                              | 12 | 4.1 | .5  | Creation of cycle frequency               | 68   |

| 2.1 Standby power supply                   |    | 4.1 | .6  | Operational commands                      | 68   |

| 2.1.1 Standby power supply circuit         |    | 4.1 | .7  | LED display                               |      |

| 2.2 Blocking oscillator type power supply  |    | 4.1 | .8  | ON/OFF function                           |      |

| 2.2.1 Primary side                         |    | 4.1 | .9  | Protective circuit                        | 68   |

| 2.2.2 Start-up                             |    | 4.1 | .10 | AV operation                              | 69   |

| 2.2.3 Normal and control operation         |    | 4.1 | .11 | SAT standby                               |      |

| 2.2.4 Protective operation                 |    | 4.1 | .12 | SAT unit control                          |      |

| 2.2.5 Power Factor Control                 |    | 4.2 |     | s systems in Q 2500 chassis               |      |

| 2.2.6 Secondary side                       |    | 4.2 |     | I <sup>2</sup> C bus systems              |      |

| 2.2.7 Voltage stabilisation                |    | 4.2 |     | IC 24C64 memory                           |      |

| 2                                          |    | 4.2 |     | EPROM M 27 C 322                          |      |

| 2                                          |    | 4.2 |     | SRAM                                      |      |

| 2.2.9 Servicing information                | 21 | 4.2 |     | Search functions                          |      |

| 2.3 Horizontal deflection and high voltage | 21 | 4.2 |     | Storage                                   |      |

| production                                 |    | 4.2 |     | Programme recall                          |      |

| 2.3.1 Horizontal driver                    |    | 4.2 |     | System clock                              |      |

| 2.4 Horizontal output stage                |    | 4.2 |     |                                           |      |

| 2.4.1 High voltage production              |    | 4.2 |     | Control of signal processing Service mode |      |

| 2.4.2 Horizontal- offset deflector         |    |     |     |                                           |      |

| 2.5 East/west correction                   |    | 4.2 |     | Video text                                |      |

| 2.5.1 Circuit                              |    | 4.2 |     | Picture signal processing                 |      |

| 2.6 Vertical output stage                  |    | 4.2 |     | Components for                            |      |

| 2.6.1 Flyback generator                    |    | 4.2 |     | Signal path                               |      |

| 2.6.2 Vertical protective circuits         |    | 4.2 |     | IC functions                              |      |

| 2.7 Beam current limitation                |    | 4.3 |     | C 3230                                    |      |

| 2.7.1 Overbeam current fuse                |    | 4.3 |     | Input interface                           |      |

| 2.7.2 HFLB protective circuit              | 34 | 4.3 |     | 20.25 MHz clock generator                 |      |

| 2.8 Speed modulator                        |    | 4.3 |     | Comb filter                               |      |

| 2.8.1 General                              | 34 | 4.3 |     | Multi-standard colour decoder             |      |

| 2.8.2 Switching of the speed modulator     | 36 | 4.3 |     | Line compression and                      |      |

| 2.9 Colour stages                          | 37 | 4.3 |     | Output format conversion                  |      |

| 2.9.1 Cut off control                      | 38 | 4.3 |     | Synchronisation block                     |      |

| 2.9.2 Switch off flash suppression         | 40 | 4.3 |     | I <sup>2</sup> C bus interface            |      |

| 2.10 Rotation panel                        | 40 | 4.4 |     | f picture memory SAA4955HL                |      |

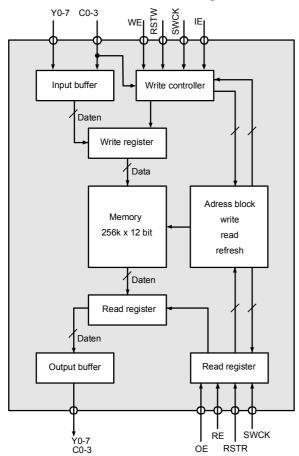

| 2.10.1 Raster correction                   |    | 4.4 |     | Storage space                             | 91   |

| 2.10.2 Circuit                             |    | 4.4 |     | Conversion of signals in                  |      |

| 2.11 NF output stages                      |    | 4.4 | .3  | Half picture memory 2 and 3               |      |

| 3 Receiver components                      |    | 4.4 | .4  | Control pulses                            | 92   |

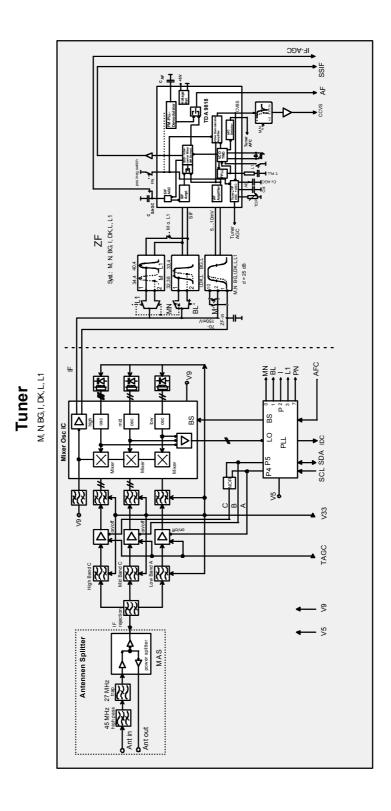

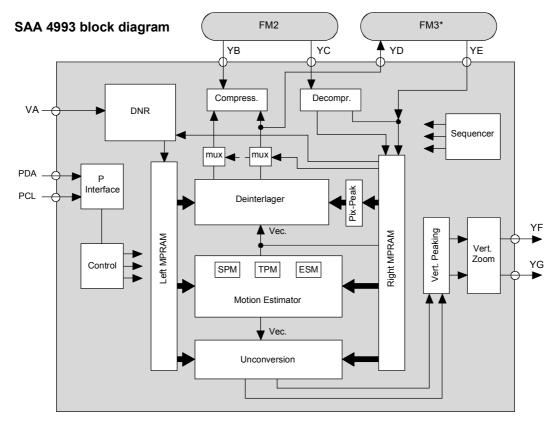

| 3.1 HF/IF unit                             |    | 4.5 | Fal | conic module SAA 4993                     | 96   |

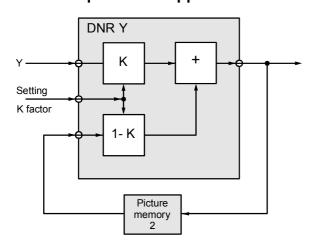

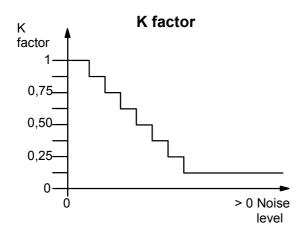

| 3.1.1 HF/IF components                     |    | 4.5 | .1  | Noise reduction                           | 96   |

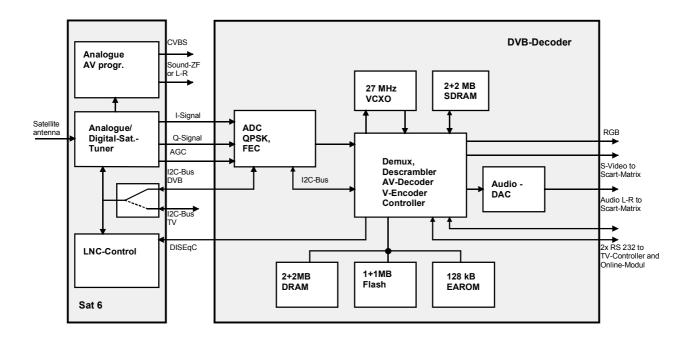

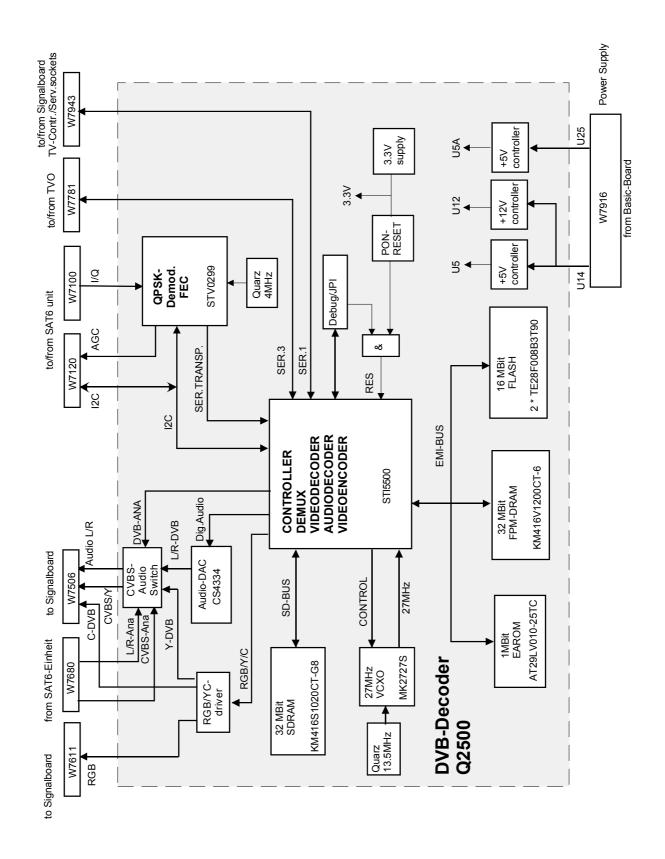

| 3.2 DVB Board                              |    | 4.5 | .2  | Line interpolation                        | 98   |

| 3.2.1 Overview                             |    | 4.5 | .3  | Movement detector                         |      |

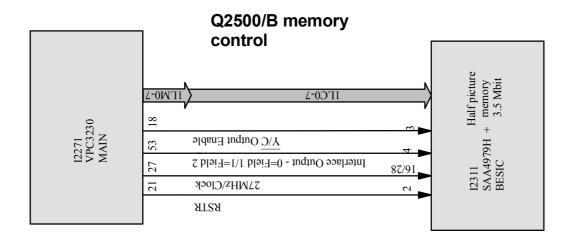

|                                            |    | 4.5 | .4  | Memory control                            |      |

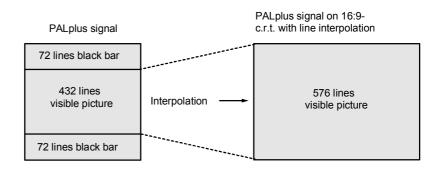

| 1                                          |    | 4.6 |     | A 4979 (BESIC)                            | 99   |

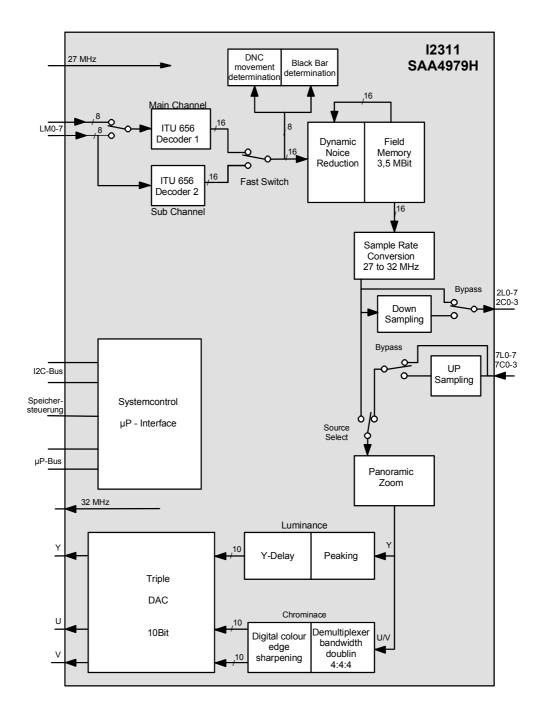

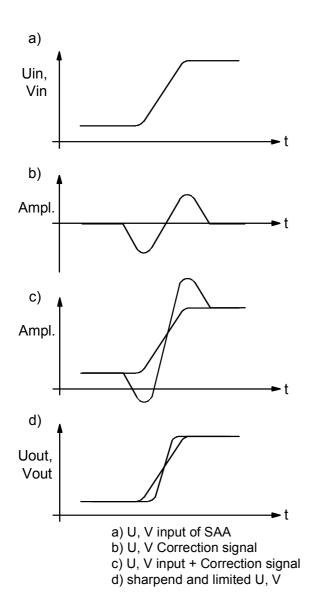

|                                            |    | 4.6 |     | Chroma branch                             |      |

| 3.3.2 DVB/TV-Features                      |    | 4.6 |     | Band width doubling                       |      |

| 3.3.3 Architecture                         |    | 4.6 |     | Colour flank sharpening                   |      |

| 3.4 Components                             |    | 4.6 |     | Y signal path                             |      |

| 3.4.1 Satellite front end                  |    | 4.6 |     | Microprocessor interface                  |      |

| 3.4.2 Functional distribution              |    | 4.6 |     | Control of the 100 Hz processing          |      |

| 3.4.3 Tuner                                | 54 | 4.0 | .0  | Control of the 100 Hz processing          | 102  |

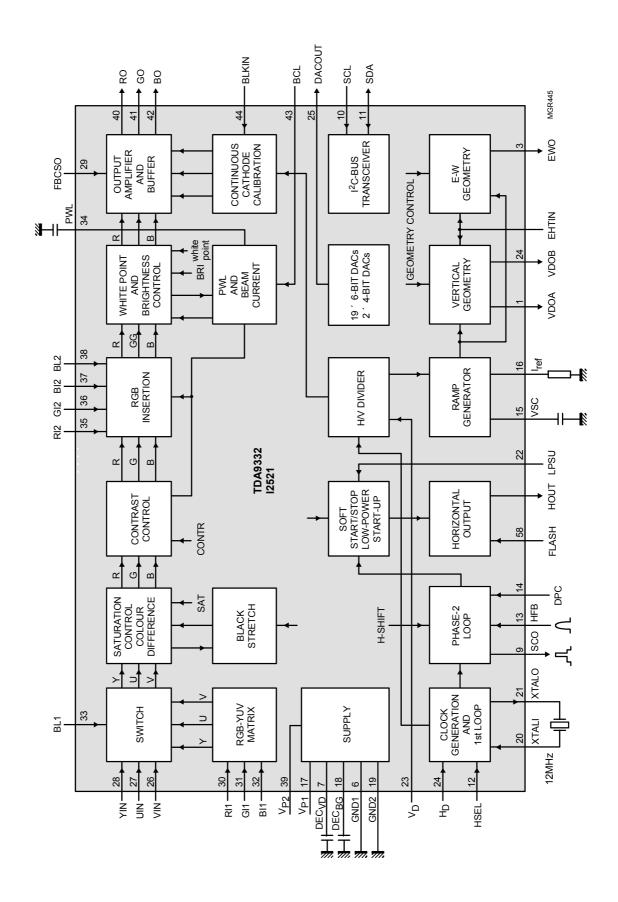

|   | 4.7 Vide    | eo/deflection processor TDA 9332/Ra | ange |

|---|-------------|-------------------------------------|------|

|   | Video/RGB   | path                                |      |

|   | 4.7.1       | Matrix circuits and signal          | 103  |

|   | 4.7.2       | Control stages                      | 105  |

|   | 4.7.3       | I <sup>2</sup> C bus interface and  | 105  |

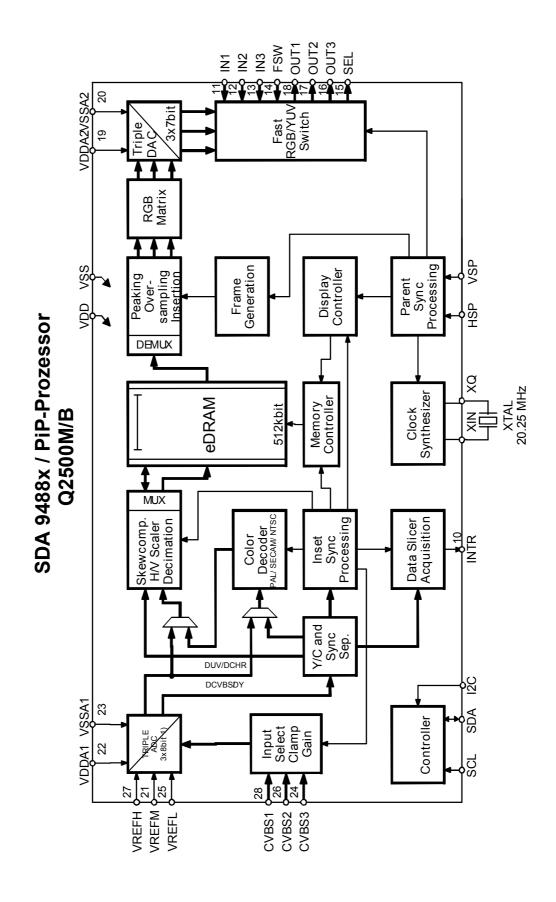

|   | 4.8 Picts   | ure in picture                      | 105  |

|   | 4.9 Vide    | eo/deflection controller TDA9332    |      |

|   | (deflection | area)                               | 108  |

|   | 4.9.1       | Clock generation/Phase 2 loop       | 108  |

|   | 4.9.2       | DAC for OW/V control                |      |

|   | 4.9.3       | Beam current dependent correction.  | 108  |

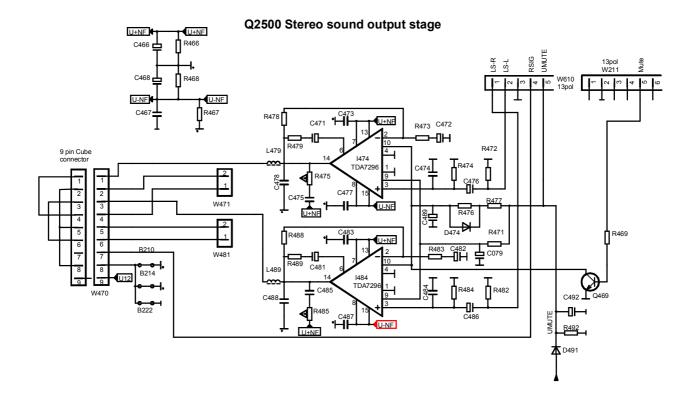

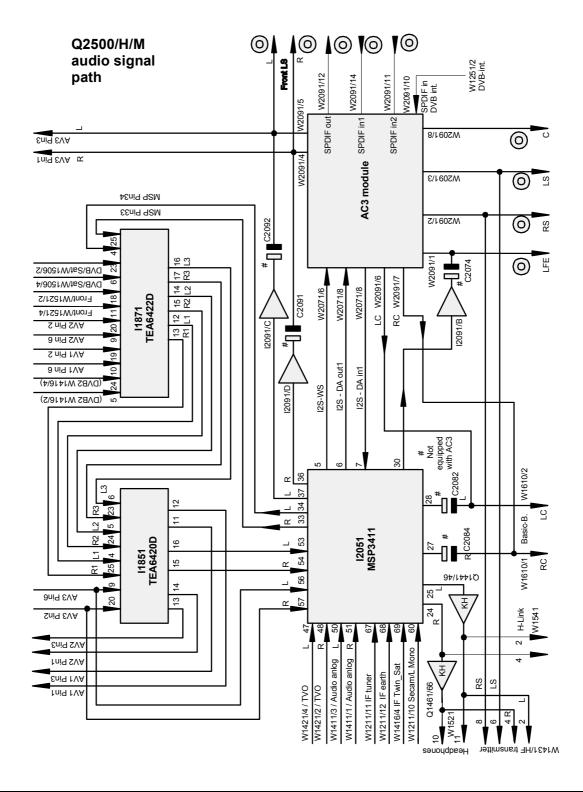

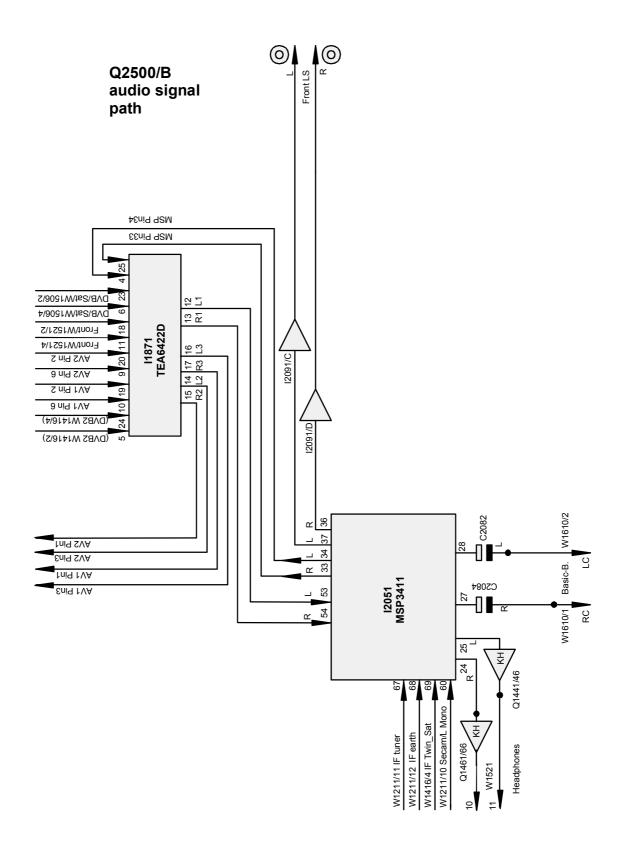

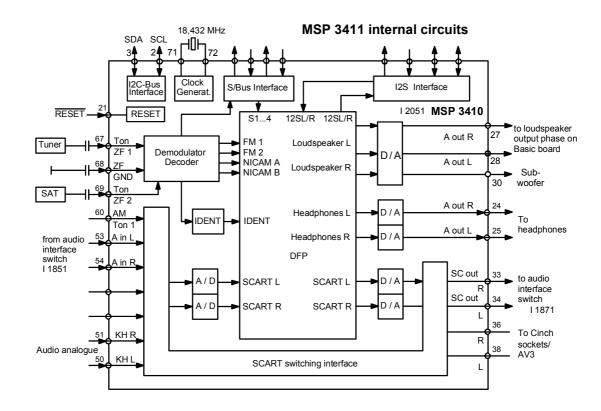

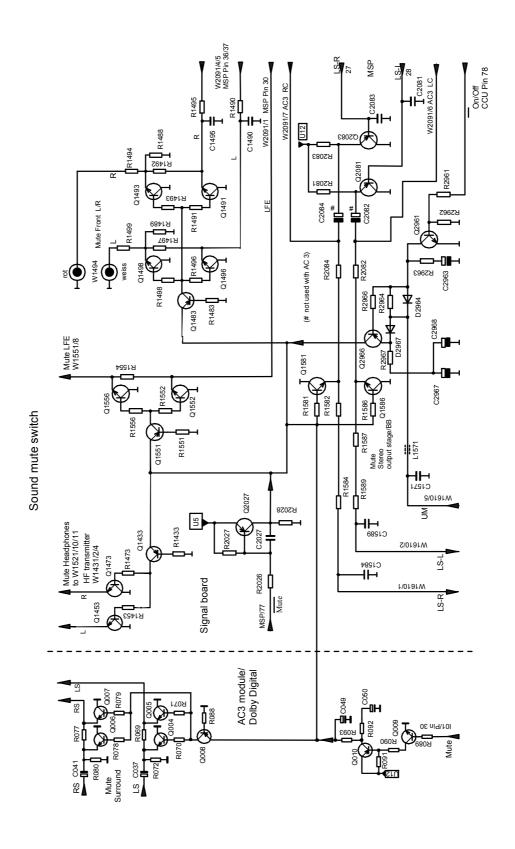

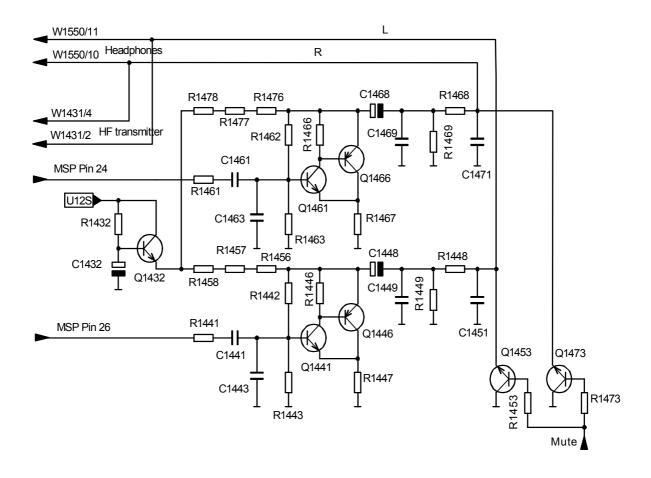

| 5 | Audio s     | ignal processing                    | .110 |

|   | 5.1 Aud     | io-Signal path Block diagram Q 250  | 0    |

|   | H/M and B.  |                                     | 110  |

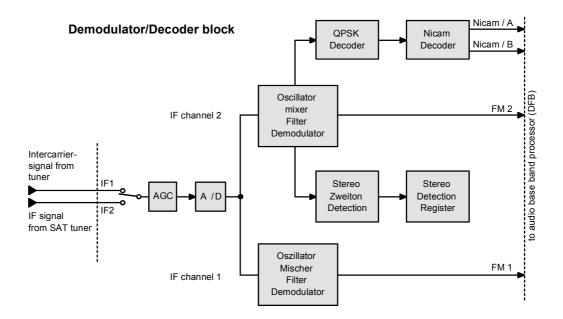

|   | 5.2 Den     | nodulator/Decoder-Block             |      |

|   | 5.2.1       | Audio baseband processing           | 113  |

|   | 5.2.2       | Demodulator/decoder block           | 113  |

|   | 5.2.3       | Nicam processing                    | 114  |

|   | 5.2.4       | Audio signals from the interface    |      |

|   | 5.2.5       | AM audio signals at L standard      | 114  |

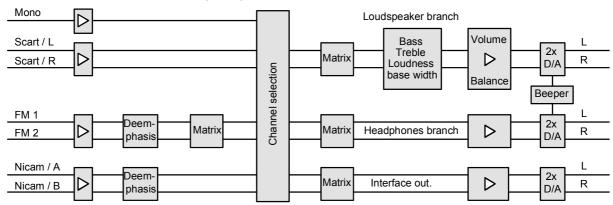

|   | 5.2.6       | Audio base band processor           | 115  |

|   | 5.2.7       | Loudspeaker branch                  | 115  |

|   | 5.2.8       | Loudness                            | 115  |

|   | 5.2.9       | Sound setting                       |      |

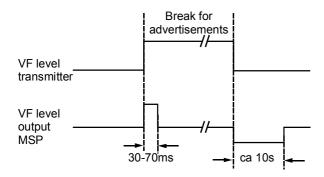

|   | 5.2.10      | Loudspeaker control and AVC         | 116  |

|   | 5.2.11      | DAC                                 | 116  |

|   | 5.2.12      | Headphone branch                    |      |

|   | 5.2.13      | Interface branch                    |      |

|   | 5.2.14      | Deadline volume                     |      |

|   | 5.2.15      | Mute circuit                        |      |

|   | 5.2.16      | Headphone amplifier                 |      |

|   | 5.3 AC3     | 3 module (Dolby Digital)            |      |

|   | 5.3.1       | Block diagram, AC3 module           |      |

|   | 5.3.2       | AC 3 signal processing              |      |

|   | 5.3.3       | AC 3 IC functions                   |      |

| R | Interfac    | e switching                         | 123  |

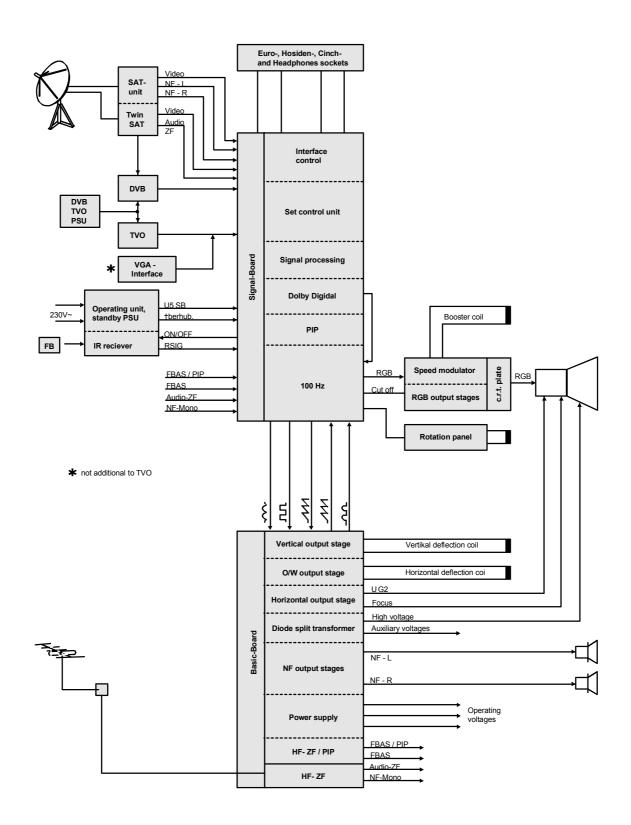

#### 1 Introduction

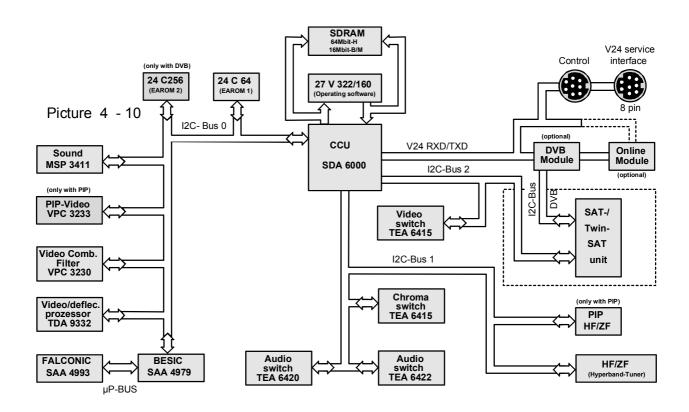

The Q 2500 chassis is a further development of the tried and tested 100 Hz Q 2400 chassis. The modular design, dimensions and layout have been retained.

In order to improve picture performance even further, several circuit components have either been modified or newly added. For sound signals, IF processing in the main receiver unit is now entirely digital.

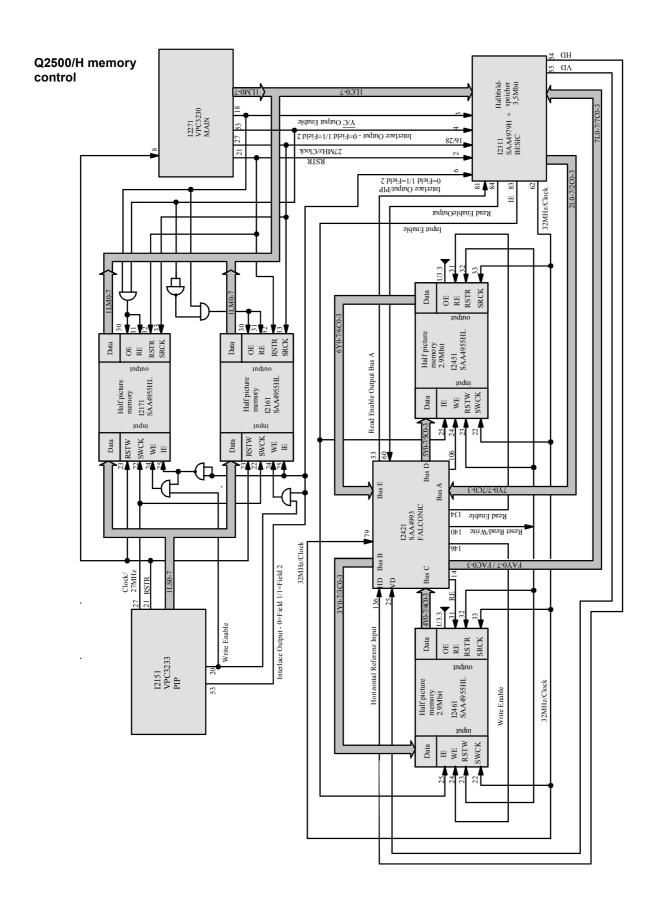

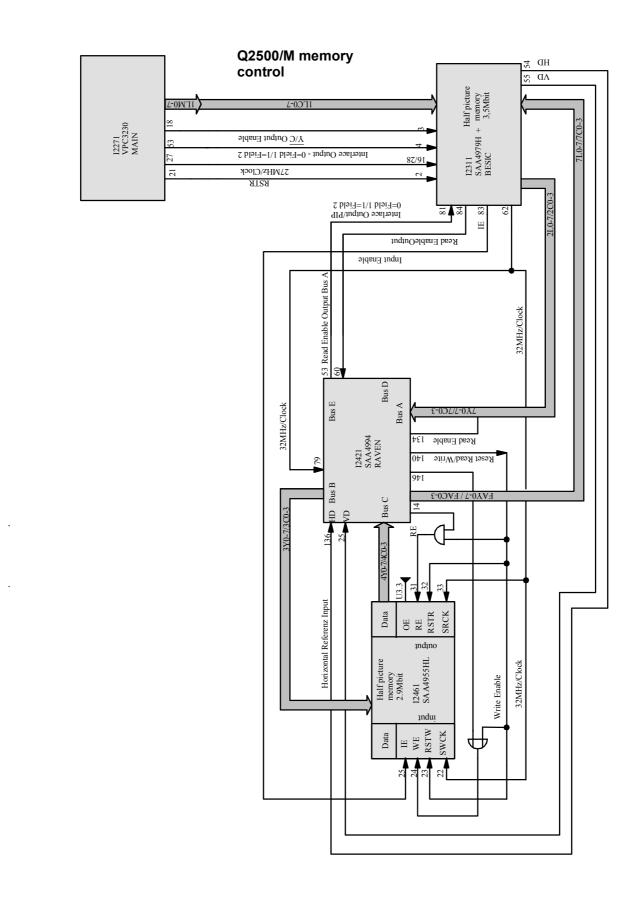

The Q 2500 chassis is available in three different versions, Q 2500/H (High End), Q 2500/M (Medium) and Q 2500/B (Basic). The signal board is different for all three versions. It has different equipment in certain areas owing to the different power spectrum of the three versions. All H/M and B signal board versions are electrically interchangeable. Due to the incorporation of 2 or 3 AV sockets (the back of the TV set does not fit) they are not mechanically compatible. Except for the signal board there is no differentiation with respect to all other components for the different versions - High End, Medium and Basic. The Q 2500 chassis therefore supersedes the Q 2400 and Q 4140 chassis completely.

Because of this concept it is now possible to fit a DVB upgrade kit to all 100 Hz TV sets – from the Contur to the Aconda. So far this has only been possible for sets with the Q 2400 chassis and not for sets with the Q 4140 chassis.

The following features have been retained from the previous chassis:

- 8 bit digital signal processing

- ACP (Automatic Channel Programming) for fully automatic programming of stations and sorting of cable and SAT reception, including an update function.

- child protection security-plus with secret code.

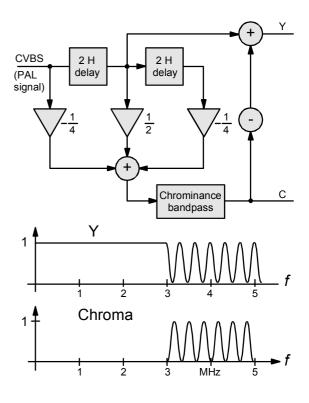

- Sharpness control, photo CD circuit and comb filter (S-PAL).

- SCS (Sharpness Control System) for a picture-dependent velocity modulation of the horizontal (line) sweep.

- DTI Plus (Digital Transient Improvement) for colour edge sharpening.

- 576-line still picture

- Adjustable noise suppression DNC (Digital Noise Control)

- Suppression of interline flicker DLC (Digital Lineflicker Control).

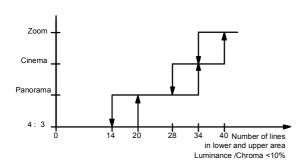

- Digital Line Interpolation (DLI) for full frame picture display for PALplus and also in all zoom modes.

- Digital Motion Interpolation (DMI) ensures continuous movement over all single frame pictures.

- Automatic Movie Detection (AMD) for switching to wide screen format in PAL standard on 16:9 units.

- Automatic PALplus recognition and format switching for 16:9 units.

- Digital Scene Control (DSC) for improved grey scales.

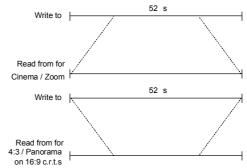

- Various switching modes (4:3, Cinema, Zoom, 16:9 and Panorama Mode for 16:9 units).

- Automatic Volume Control (AVC) for adjusting the volume between different channels and during commercial breaks

- On the front: Headphone output and input with S terminals and three cinch sockets.

- Copy function for re-recording between different inputs and outputs (also in standby mode), and during TV programmes.

- Internal clock synchronized with Teletext.

- EPG function (electronic programme guide).

- Recording timer for video recorder and SAT standby function.

- Operation of Loewe video recorders via the menu.

- Switch-off automation and timer.

- In 81 cm sets a rotary panel is used in order to compensate for the earth's magnetic field. This prevents distortion of the picture no matter where the set is placed.

- Personal Control System (PCS): operation tailored to individual customer requirements. The most frequently used functions may be assigned to four buttons of the remote control. Additionally, the operating manual may be viewed on the screen - On Screen Display (OSD). This includes help instructions on functions currently used, information on the remote control functions and an index, which enables immediate implementation of functions. It is also possible to set limitations to the scope of operation according to customer requirements. The user may, for example, be prevented from making changes to particular settings.

- Automatic Gain Control (AGC) for all video signals shown in the main picture.

- The RGB signals are no longer converted to analogue Y/C signals but are directly digitised instead.

- An Audio-In socket to which, for example, an external digital radio receiver may be connected.

- Some models, e.g. Aconda, may be upgraded

- A Dolby Digital Module can be installed in model versions H and M.

- The EAROM and the DVB software may be directly written to via an external V 24 service interface using a PC and service adapter.

The following features are completely new:

- Depending on version, either two or three AV sockets.

- Depending on version, a Teletext memory with 3000 pages (with active EPG function 2000 pages).

- An own radio menu, accessible over the "speaker symbol" on the remote control.

- Improved Digital Movie Mode (DMM). Feature films are recognized safely. Therefore, accidental switching to camera mode is prevented. Switching effects do not occur anymore.

The following circuit descriptions have been subdivided according to the individual modules. Deviation from this scheme occurs occasionally in order to emphasize relations between circuits more effectively. All component positions in the circuit diagrams are identified by four figures. For the signal board the fully equipped version H is explained. For versions M and B only the differences are noted.

The upgrade kits are explained in a separate circuit description.

#### 1.1 Foundations of 100 Hz technology

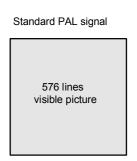

#### 1.1.1 Prerequisites for 100 Hz

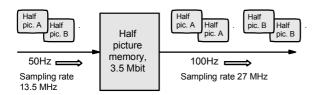

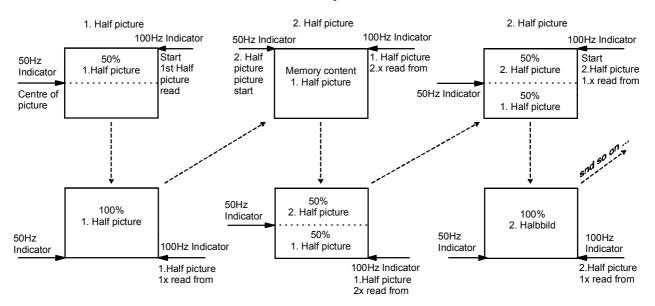

In order to double the picture frequency at the receiver, the signals have to be read into the relevant memory blocks and then read out twice at double rate.

The following prerequisites must be met:

- The signals need to be digitised.

- The memory modules require at least 3 Mbits storage capacity.

- The software must be able to run a controller, which in turn monitors the read-in and read-out functioning of the memory.

- Suitable frequency-stabilized oscillators for generating the clock frequency must be provided.

- The drive signals for the output stages, line and field deflection, and the E/W correction must also be at double frequency.

- The power output stages for deflection, as well as the deflector itself, need to be designed for the higher frequency and the resulting higher currents.

- The RGB output stages need to be able to process the doubled bandwidth.

#### 1.1.2 100 Hz display modes

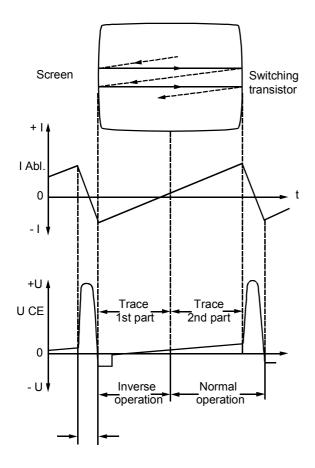

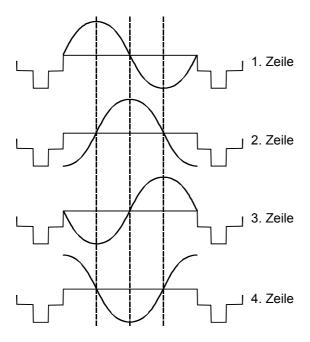

When examining display modes the deflection raster and the video raster need to be considered together. In 50 hz operation, the two single-frame pictures A and B are written to the scanning system 'a' and 'b', i.e. every second line of frame A and the intermediate lines of B. This is achieved in that the flyback of 'a' begins in the middle of a line. Trace 'b' starts also in the middle of a line but is written to the end of a complete line. The next trace 'a' starts again at the beginning of a line. The trace time, however, is always the same.

#### 1.1.3 Mode AABB

The simplest case of 100 hz operation involves a simple doubling of single-frame picture display, i.e. field A is displayed twice consecutively followed by field B (AABB).

To achieve this the deflection raster must be modified so that ,a' is written twice followed by 'b' (aabb). Theoretically, this can be accomplished in two ways. Firstly, by adjusting the flyback's starting time for the 4 single frames. A half-line more is written for 'a1' and a half-line less in for the third field. In practice, such a scheme would be quite difficult to implement. In comparison, the second possibility is easier to achieve. This involves shifting the 2<sup>nd</sup> and 3<sup>rd</sup> fields (a2 and b1). This can be accomplished by adjusting the current though the deflector by modifying the base resistance. This produces the same time interval for all traces over all fields

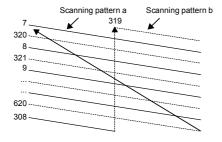

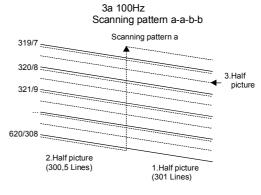

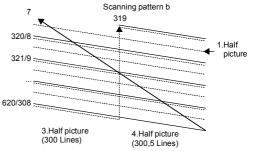

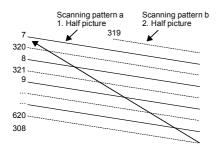

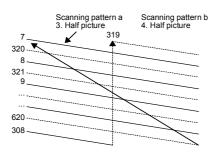

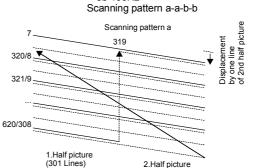

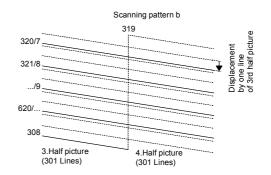

#### **Deflection 100Hz**

1. 50Hz

2.100Hz Scanning pattern a-b-a-b

2.Half picture

3b 100Hz

For AA and BB display, delay lines must ensure that the lines of the 1st and 2nd, and 3rd and 4th fields contain the same picture information when superimposed on one another. This mode of display allows for very effective reduction of large-area flicker. A reduction of interline flicker is, however, not possible, because intermediate lines are only traced after 20ms.

#### 1.1.4 Mode ABAB

This mode, together with the two described below, are only possible in conjunction with a second single-frame picture memory because of the alternating display of A and B. The deflection must also operate in 'abab' raster form. In this display mode, the signals are not modified during deflection or image processing operations. In this case, both interline flicker and large area-flicker can be reduced. However, jerking effects in moving images can arise. This form of display is only suitable for signals where an image is formed from two fields between which there is no relative movement. This mode is therefore of interest only for "Photo CD" or cinema scope films in PALplus.

Reduction of interline flicker without movement interpolation (DLC)

| Memory 1 | Memory 1 retarded | Memory 2 | Output | Deflection<br>Scanning<br>pattern |

|----------|-------------------|----------|--------|-----------------------------------|

| Α        | A۷                | В        | Α      | а                                 |

| Α        | A۷                | Α        | A'     | b                                 |

| В        | В٧                | Α        | B'     | а                                 |

| В        | В٧                | В        | В      | b                                 |

| Α        | A۷                | В        | Α      | а                                 |

#### 1.1.5 Mode AA'B'B

In this display mode two single-frame pictures, A' and B', are calculated. By using an interpolation filter the current single-frame, the current single-frame delayed by one line and the

signal delayed by one single-frame are compared with one another. If deviations are de-

Interpolation example

| Memory 1          | 10 | 10 | 10 | xxx |

|-------------------|----|----|----|-----|

| Memory 1 retarded | 10 | 10 | 9  | xxx |

| Memory 2          | 10 | 8  | 8  | xxx |

| Output            | 10 | 10 | 9  | xxx |

tected in one of the signals, this signal is eliminated and the values that agree in the other two signals are retained. If all three signals vary, an average is formed.

The deflection proceeds as sweep 'abab'. The calculated A' and B' are written to shifted scanning system of the 2<sup>nd</sup> and 3<sup>rd</sup> single frames. A and B are written to the non-shifted system of frames 1 and 4.

This mode is suitable for the display of horizontal motion between frames. Only small jerking effects arise between movements.

The mode is used to suppress interline flicker in normal TV operation.

#### 1.1.6 Mode AA\*BB\*

In this display mode with respect to the calculated frames A\* and B\*, the movement between the original frames A and B, and between B and the next A are taken into account. This movement interpolation (DMI – Digital Motion Interpolation) takes into account both horizontal and vertical movements which cover several lines. This means that when suppressing interline flicker, continuous movement over all frames is achieved.

For full frame pictures (films) it is also assured that no movement between two single-frame pictures takes place (DMM – Digital Movie Mode).

In this display mode the deflection is also 'abab'.

#### **Movement interpolation**

Picture 2

Picture 3

Picture 1

Picture 1\*

Picture 2

Picture 2\*

Picture 3

Picture 3\*

#### Display mode 100Hz

| No. | Picture<br>change<br>frequency | Video<br>scanning<br>pattern | Deflection<br>scanning<br>pattern | Mode                                   | Advantages                                                                                                                            |

|-----|--------------------------------|------------------------------|-----------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 1.  | 50Hz                           | A-B                          | a-b                               |                                        |                                                                                                                                       |

| 2.  | 100Hz                          | A-A-B-B                      | a-a-b-b                           | DLC off                                | -Reduction of large area shimmer                                                                                                      |

| 3.  | 100Hz                          | A-B-A-B                      | a-b-a-b                           | -Photo CD on<br>-PAL plus Cinema Scope | -Reduction of large area shimmer<br>-Reduction of interline shimmer<br>in full picture setup                                          |

| 4.  | 100Hz                          | A-A´-B´-B                    | abab                              | DLC on                                 | -Reduction of large area shimmer<br>-Reduction of interline shimmer in full<br>picture setup with movement                            |

| 5.  | 100Hz                          | A-A*-B*-B                    | abab                              | DMI                                    | -Reduction of large area shimmer<br>-Reduction of interline shimmer in full<br>picture setup with movement<br>-Movement interpolation |

#### 2 Basic board

This main heading covers the analogue stages from the power supply circuit through the power output stages to beam current limitation, irrespective of whether or not they are contained on the basic board. In order to maintain consistency, several smaller stages on the basic board are also described.

#### 2.1 Standby power supply

The Q 2500 receiver once again contains a standby power supply circuit, thus limiting current consumption in this mode to < 2 Watt.

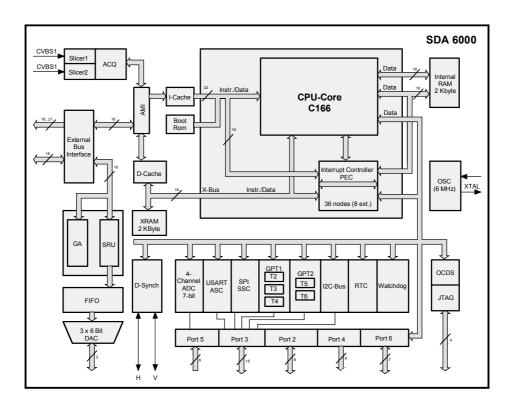

The use of a new CCU SDA 6000 on the signal board increases the standby power consumption from 1 W to 2 W, compared to the older model. To meet the requirements of increased power consumption, there is now a small, blocking oscillator type power supply attached to the operating control, which supplies the U5 SB.

Siemens Corporation has announced a new index of the SDA 6000, that needs only 1 W power in standby operation. This will be implemented on the signal board, but the standby power supply will not be changed.

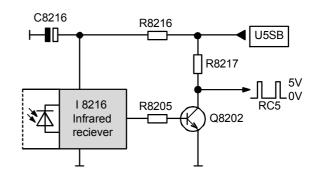

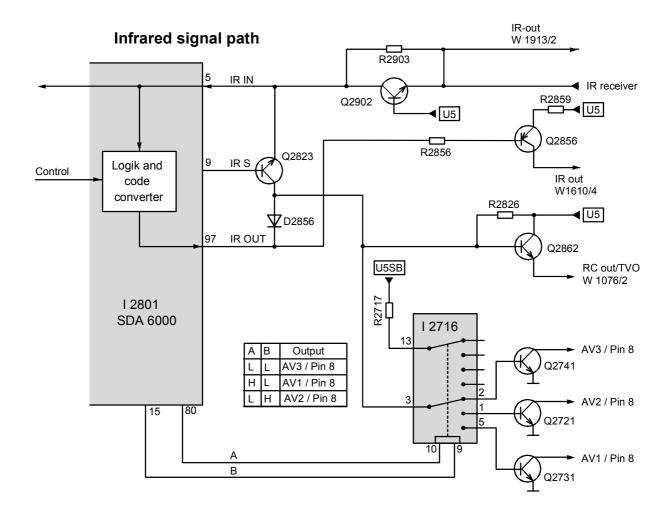

The circuit itself is mounted together with the IR receiver and the LEDs on its printed circuit board. It supplies the U5 SB, which maintains functioning of the IR detector, the processor circuit and the operating software. The last two circuits operate in standby mode, i.e. the clock frequency is reduced internally so that only those stages required to recognize a switch-on command are maintained in operation. Because of the NexTView function with U 3.3 the TV RAM is retained in self refresh

mode. All of this contributes to the standby mode's low power consumption.

#### 2.1.1 Standby power supply circuit

The main voltage is fed via W 8103 the switch S 8101 and W 8611 to the basic board and continues via the line filter (C 612, T612,C 613) and the 3-pole pin connector W613/BB back to pin 2/3 of operating control W 8613. The 220V is rectified by the bridge rectifier D 8133 and smoothed by C 8133. The blocking oscillator type power supply consists essentially of the control circuit I 8131, in which the switching transistor for the primary blocking oscillator winding is integrated, the transformer T 8101 and the opto-coupler I 8122. An operating voltage of about 18V is led from winding T 8101 pin1/2 via D 8138/D 8131 and C 8132 to I 8131 on pin 4. Control input I 8131 pin 3 is supplied with secondary side current control information by opto-coupler I8122. This control circuit stabilises the secondary side output voltage derived from the winding pin 5/8 of T 8101 at 5V. This is then fed via W 8181 pin 8 to the signal board. I8122 is fitted with an internal excess temperature, excess current and excess voltage switch protection. The blocking oscillator type power supply operates at a switching frequency of about 50 kHz.

## T8 101 Standby transformer MP04 D8 121 D8 123 D8 133 D8 133 D8 134 D8 134 D8 135 D8 135 D8 134 D8 137 D8 137 D8 137 D8 137 D8 137 D8 137 D8 138 D8 1

#### **Q2500 Operating Control**

The rectified secondary voltage is applied to pin 2 of the relay winding L 8101. via protective resistor R 106. The cold end is open since Q114 is non-conducting and the receiver is in standby mode. This is indicated by illumination of the red LED.

Transistor Q 8114 is blocked, if the working contact is open, the device is in standby, which is indicated by illumination of the red LED.

If the processor receives an ON command from the infrared detector it sets its appropriate switch output to low level. This is then fed to the base of Q 8111 via pin 5 in plug W 8181 which is blocked. Via R 813, U5 SB makes transistor Q 8114 switch. The cold end of the relay coil is earthed, the working contact is closed and the main voltage flows to the main power supply circuit via pin 1 of W 8613, thereby switching the receiver on.

## 2.2 Blocking oscillator type power supply

The voltage supply in the Q 2400 chassis is drawn once again from a free-running blocking oscillator type power supply. TDA 4605 is used as the control and regulating circuit. In terms of its function, this IC resembles the well-known TDA 4601.

It has, however, a different type of output stage. The 4605 is designed to control a field effect transistor.

This circuit uses a BUZ 91 MOS-FET as the switching transistor. Since control of field effect transistors requires virtually no current, reducing the need for heat dissipation, it has been possible to eliminate the heat sink in the TDA 4605 control IC and house the circuit in a dual-in-line package.

On the secondary side, BUZ 71 A V-MOS transistors are used to stabilise U3.3, U5 and U12 in order to keep power dissipation to a minimum.

The converter transformer, which also provides the standard VDE power distribution, has a primary working winding and a secondary winding to supply voltage to the IC and to generate a control voltage.

Secondary windings also generate the following voltages:

UB to supply the line output stage

U 25 to supply the line driver stage

U 3.3, U 5 and U 12 predominantly to supply an operating voltage to the digital control

U9 for the interface switching ICs

U8 for the video ICs

UNF+ and UNFused to supply a floating voltage to the VF output stages, approx. <u>+</u> 18 V

#### 2.2.1 Primary side

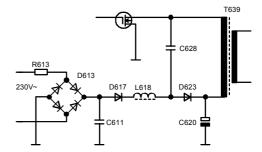

The mains voltage flows through the mains power switch, the working contact of the standby relay and the mains RFI suppression filter to the degaussing coil, and via the start-up current limiter R 613 to the bridge rectifier D613

A voltage of approx. 310 V very rapidly builds up at charging capacitor C 620. This is applied to the drain terminal on the switching transistor via the working winding in the converter transformer.

Since the gate BUZ 91 is not driven at this time, there is no load on the operating voltage.

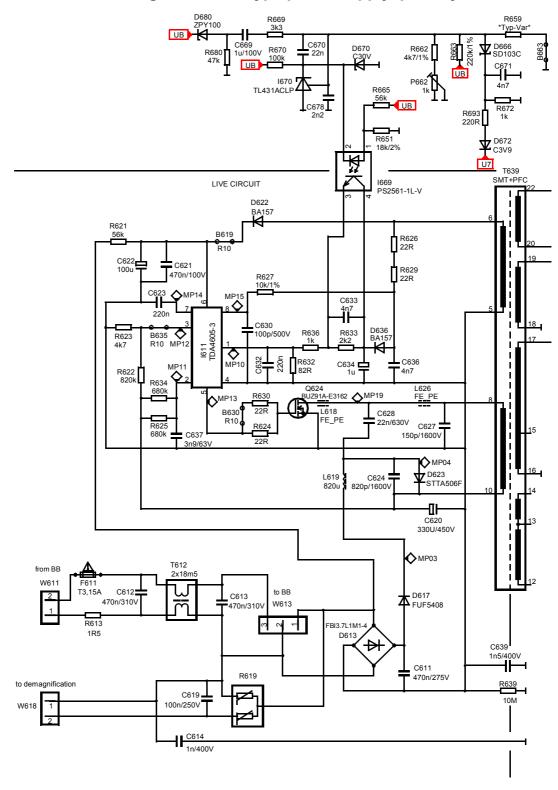

#### Q2500 blockingo oscillator type power supply, primary side

#### 2.2.2 Start-up

The power supply section is started up by an additional starting circuit. The required voltage is rectified using a diode path in the bridge rectifier. It is fed via resistor R 621 to pin 6 in TDA4605 where capacitor C 622 is then slowly charged. During this charging phase, capacitor C 637 is charged to 6.6 V on pin 2 via an internal IC path. A reference voltage of 1V that is required during the start-up phase and later during normal operation is also generated in the IC.

If the voltage at pin 6 reaches 12 V the IC operates and makes the switching transistor conducting via pin 5. A current flows through both the transformer working winding and the switching transformer drain source path. During this period, magnetic energy is being stored in the transformer. During this conductive phase, a drain current simulator C 637, integrated in the IC, is charged on pin 2. If the internal reference value of 1 V is reached the IC blocks the switching transistor. The magnetic field in the transformer breaks down and this induces voltages in the windings.

The start-up procedure recommences and the system swings/oscillates to normal operation. This is arrived at when a voltage of 400 mV has built up at pin 1.

#### 2.2.3 Normal and control operation

A static state is set in normal operation at constant load. The operating voltage for the IC is drawn from the transformer winding pin 5-6 and rectified with D622. The voltage at pin 6 in the IC is then 11 V. The control input at pin 1 is 400 mV and the duty cycle for the zero passage detector at pin 8 in the IC is set.

The switching transistor is controlled with a fixed frequency of between 20 and 40 kHz, which corresponds to the instantaneous load.

If the load changes, the duty cycle at pin 8 in the IC also changes. The negative edge indicates to the IC when the energy stored in the transformer has been dissipated. If the load increases, this occurs more quickly and the IC reduces the control frequency. If the load decreases, the control frequency increases. This means that load variations between approx. 40 and 260 W and mains voltage fluctuations between 180 and 270 V can be compensated for.

In order to achieve a higher UB voltage stability, regulation on the secondary side is now used which influences the primary circuit's I 669 opto-coupler. The I 669 opto-coupler is controlled via I 670. The control mechanism is influenced via several paths:

- With d.c. voltage via R 663

- Alternating, by coupling to the R 680 diode.

- When not under load, via D 672

The operating voltage is set with the P662 potentiometer. A small resistance here indicates a high value of UB. Correspondingly, a high value of R means a low value for UB.

If UB increases, e.g. due to a smaller load on the line output stage, UB exerts a stronger influence via R 663 at the input of I 670. This results in the I 670 cathode outputting a smaller voltage. The photodiode in I 669 receives more current through R 665. The path between pin 3/4 of I 669 has a lower resistance allowing for a higher voltage on pin 1 of I 611. Component I 611 then regulates output voltage until a value of 400 mV on pin 1 is reached again. If the value of UB becomes lower, then the regulation process is exactly the inverse of that described here.

Via D 680, R 669 and C 669, ripple voltage components are coupled into the regulating circuit. In particular, this branch prevents a low 50 hz ripple voltage arising on UB. With 60 hz signal sources (NTSC, PAL 60 Hz or VGA operation), this would result in humming interference in the picture.

Without secondary-side regulation, e.g. in SAT standby operation, UB would increase to approx. 180 V. In this mode of operation, other voltages (e.g. the bias voltages for the U 5, U 12 branch) do not alter significantly. Stabilization is also guaranteed for these voltages in this mode of operation.

Due to the secondary-side stabilization with UB as stabilization factor, UB without any load would naturally remain constant. In this case, the power supply would regulate down from approx. 180 V (without secondary-side regulation) to the previously set value of UB, typically 146 V. This would also result in all other voltages being reduced. The bias voltages for the stabilized voltages would be too low and they would no longer be stabilized. The digital electronics would search for errors.

In order to prevent this, the regulation acts via U 7. This is accomplished via components D 672, R 693 and 666.

U 7 also drops when the line-output stage is disconnected. When this has reached a value of approx. 6V, the D 666 Schottky diode voltage has also fallen sufficiently for it becomes conducting. A further drop in operating voltage is prevented by the I 670 input. Stabilization of secondary side voltages, e.g. for U 5 and U 12, still operate properly in this mode of operation.

The indicator for this is the voltage on pin 6 in TDA4605. During normal operation this voltage is approx. 11 V. If the load increases, due to a short circuit on the secondary side, for example, the voltage on pin 6 drops. If it drops below 7V, the logic circuit switches off. The same occurs if the voltage on pin 6 exceeds 15 V due to complete discharge or a fault in the control circuit. There is also a second protective circuit to safeguard against overloading. If the current flowing through the working winding in the transformer and therefore also through the switching transistor is so great that the voltage on pin 3 drops below 1 V, the power supply also cuts out.

In addition, integrated thermal protection switches the system off at chip temperatures of over 150°.

#### 2.2.5 Power Factor Control

All TV sets with power consumption of more than 75 W, and delivered after 01.01.2001, must be fitted with a Power Factor Control (PFC) circuit.

The circuit power supplies used up to now overlay a pulsed current on the sinusoidal mains alternating voltage. The Power Factor Control circuit ensures current extraction is almost completely sinusoidal. This function is implemented by changing the power supply's input range

#### 2.2.4 Protective operation

The IC contains a protective circuit to prevent the control frequency from entering ranges where it would otherwise damage the switching transistor during over- and underload. In such cases the system is shut down.

#### **Power Factor Control**

The alternating voltage from the mains is rectified by the D 613 bridge rectifier. When in resonance, C 620 is loaded to approx. 310 V. Without PFC this means that mains current will only be drawn when the sinusoidal half-wave exceeds 310 V. Sinusoidal current extraction is therefore not guaranteed. With the PFC circuit, C 620 is not directly charged from the mains. Charging of C 620 is via the C 628 current pump. When the Q 624 switching transistor is conducting, C 628 is connected to earth. C 628 is charged via D 617 and L 619. If Q 624 is now switched off, a voltage of approx. 400 V is set on the drain.

The energy stored both in C 628 and in the coil can now charge up C 620 via D 623. C 628 will naturally also be charged when the sinusoidal mains alternating voltage just crosses zero and has a low value.

Q 624 is switched with a frequency between 20 kHz and 40 kHz, depending on load conditions. This also means that C 620 is charged with a current at the same frequency. The current drawn from the mains would also correspond to this frequency, but will be harmonized by the mains input filter.

#### 2.2.6 Secondary side

Although the secondary side voltages are relatively stable, and fast and transient changes in load can be compensated for by the field effect transistor in the primary side, stabilisation of voltages in the digital component is still required.

The two secondary voltages U 3.3, U 5, U 8, U 9 and U 12 are stabilised

For the other secondary voltages:

- UB for the horizontal stage

- U 25 for the horizontal driver stage

- UNF+ and UNF- for the VF output stage

Stabilisation is not required, as no current is drawn from these non-controlled levels.

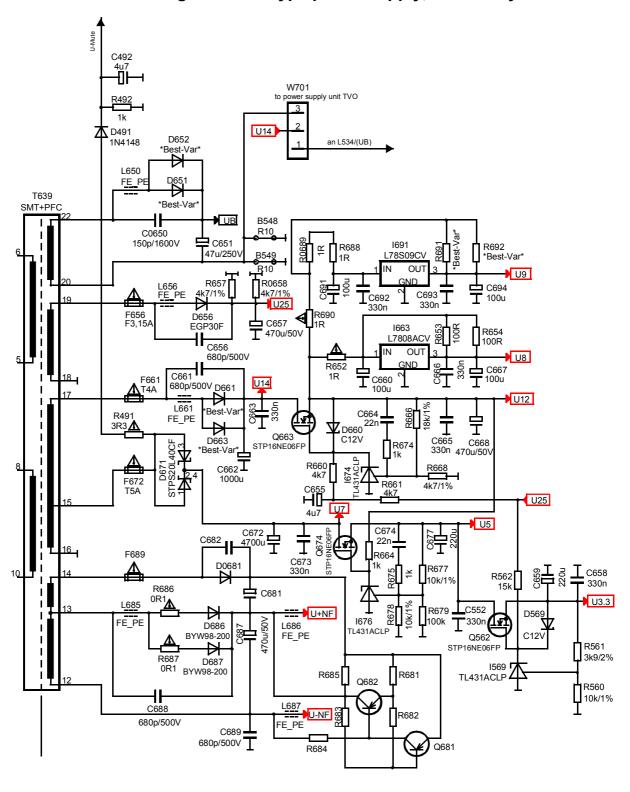

#### Q2500 blocking oscillator type power supply, secondary side

#### 2.2.7 Voltage stabilisation

For each of the operating voltages U 3.3, U 5 and U 12 a V-MOS transistor is used as a horizontal controller for stabilisation. Their gate voltages are kept constant by the connected IC's I 569 for 3.3 V, I 676 for 5 V and I 674 for 12 V. In addition, their control input is connected to the voltage distributor by the respective output voltage.

If the output voltage falls under high load, the IC's become high resistant causing the gate voltage to increase and the horizontal controllers are controlled upwards further, whereupon the output voltage increases again. If the load decreases the opposite occurs.

In addition, voltages U8 for the video control and U9 for the interface with the fixed voltage controllers L 7808 and L 78S09 are stabilised. The controllers I 663 and I 691 are now also located in the power supply. The input voltage is U 12.

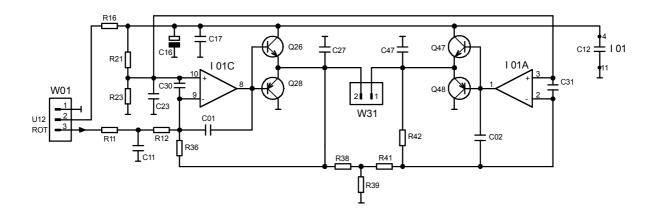

#### 2.2.8 Voltage increase

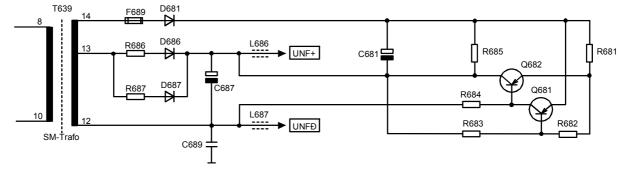

To avoid overloading the VF output phases, they are supplied with a load-dependent operating voltage. The control range of the circuit for this lies between <u>+</u>18 V in no-load operation and <u>+</u>13 V at full load.

The pulses taken from pin 14 of the transformer are rectified by D 681 and applied to the emitter connections of transistors Q 682 and Q681. For no-load or low-load operation no voltage is felt across current measurement resistor R 681. This means that Q 681 is blocked and Q 682 is switched through to its base with L level via R 684. The voltage from pin 14 of the transformer increases the VF operating voltage to +18 V.

If the noise level is increased, more current is drawn accordingly. There is a corresponding voltage drop across R 681, which means the base of Q 681 goes more negative, the transistor switches and as a consequence with base Q 682 going positive, a greater or lesser degree of blocking is achieved. The VF operating voltage is reduced accordingly.

Harmonic distortion is therefore kept low. thus preventing overheating of the output ICs. In this way a noise-level dependent video pumping can be prevented.

#### Voltage increase for VF

#### 2.2.9 Servicing information

For repairs and fault-finding in the power supply unit the following should be noted:

Always connect the unit via an isolation transformer, especially when fault finding the primary side.

The load on C 620 remains active long after the unit has been switched off. Discharge the load if necessary via a low-resistance resistor.

Operation of the power supply unit without the digital unit is possible. For this pin 5 on pin connector W 8181 is connected to earth, but not until a voltage is applied to the standby power supply. For specific failures, this test can also be done with an integrated digital component.

A check of the horizontal output stage cannot be made by withdrawing the deflection plug. For this test L 534 must be unsoldered. An extra load is not required.

A separate test of the power supply unit function without interference from the chassis can be achieved by unsoldering one side of the secondary side rectifier diodes. The rectifier branch for the UB (D 651) and U7 (671) must be available. The UB can then be loaded with a 100 Watt LED.

U 7 and UB are necessary for power supply control, so do not deactivate them.

## 2.3 Horizontal deflection and high voltage production

On the 100 Hz Chassis Q 2500 the horizontal driver, horizontal output stage and high voltage production are essentially the same as the predecessor.

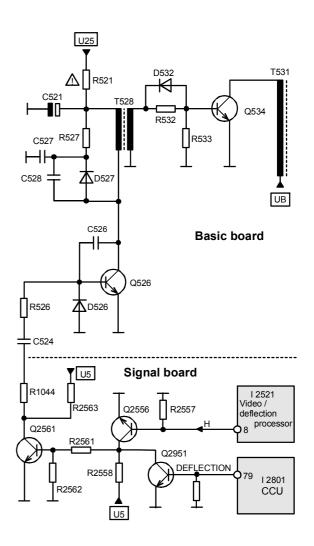

#### 2.3.1 Horizontal driver

The horizontal driver stage is controlled from I 2521 on the signal board via pin 13 from connector W 1511. The pulse at this point is 2.5 Vss.

Capacitive control via C 524 prevents driver stage Q 526 being held conductive continuously if components are faulty or there are no control pulses. Diode D 526 enables rapid discharge of C 524, if Q 526 is controlled in the blocking phase.

It can be clearly determined from the line driver circuit, as from the control of the line output stage, that this is a case of low-resistance current control. The driver stage is equipped with a transistor, which supplies for the drive transformer T 528 (conversion ratio 7:1) output stage the required base control current of up to 0.9 Ass. To limit inductive switching peaks an R/C combination is connected, a.c. to earth, to the collector of Q 526 after diode D 527. The driver stage operates with respect to the output stage in alternating operation, i.e. if Q 526 is conducting, then Q 534 is blocked and vice versa.

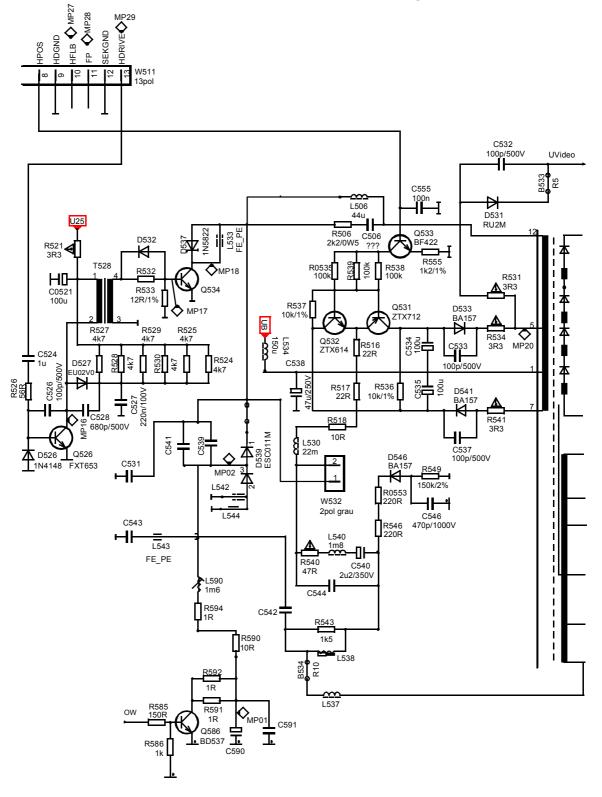

#### 2.4 Horizontal output stage

As mentioned in the previous section control of the horizontal output stage, or more precisely the horizontal switching transistor, alternates according to the switching regulator principle. Essentially the base resistance consists of R 532 and the series secondary winding of the driver transformer T 528. The paral-

lel arranged resistor R 533 dampens switching peaks arising in the inductivity.

An additional anti-parallel diode from collector Q 534 to earth, which was used as a booster diode in earlier forms of thyristor deflection switching, is not required, as in this switching concept the collector-base route of the switching transistor Q 534 fulfils the function of the booster diode by a process of inverse operation. In practice the parallel O/W-modulation diodes cause a perceptible load reduction of the switching transistor. The drawing below shows that this inverse operation of the transistor occurs during the first half of the trace, until about the middle of the line. In the second half of the run the transistor operates as normal with conducting base-emitter diode. Only during the relatively short flyback time is the switching transistor blocked. The low resistance base switching already described enables the base peak current between +0.9 A and -0.9 A in both directions to be dissipated quickly.

#### Q2500 horizontal output stage

It is conceivable that the essentially higher emitter currents (IE max. = 4.5 A) will invoke enormous "flooding" of charge carriers in the N-P- and P-N-transitions of the semiconductor. In order to guarantee rapid switching behaviour and to ensure rapid discharge of the charge carriers in the base zone, the base control is correspondingly low resistance.

In this respect it must be mentioned that the control pulses are specially formed for the dual functionality of Q 534 normal and inverse operation. In principle the trace relationship of the base control of 6  $\mu$ s flyback and 26  $\mu$ s trace time is changed to 14  $\mu$ s flyback and 18  $\mu$ s trace time. In this way it is possible, to process unavoidable production dispersion of the driver transformer. By means of prompt control the switching transistor has sufficient time to prepare for the following operational phase.

The operating voltage of the horizontal output stage is taken from the switch mode power supply and is 146 V for 33"/4:3 and

32"/16:9/RF c.r.t.s, 142V at 21,24,28"/4:3 and 136 V for all other c.r.t.s. The exact control and switching rhythm during a line period corresponds to the principle of the switched resonant circuit. For this the line switching transistor operates via its three operating conditions - conduction, inverse conduction and blocked – in such a way that the charge and discharge procedures of the collector capacity C 531 and inductivity T 531 determine the exact trace and flyback intervals.

Only during the horizontal flyback time is Q 534 blocked for 6 µs. By charging the operating voltage the capacitor of the parallel resonance circuit C 531 forms the positive half wave of a sinusoidal oscillation. C 531 and T 531 are dimensioned in such a way that they create horizontal flyback pulses. The natural desire of a parallel resonance circuit to convert the stored charge in the capacitor into inductance as magnetic energy leads to reversal of polarity of the current.

Normally the negative component of the sinosoidal oscillation is felt on the collector of Q 534. This attempt is however prevented by the collector-base diode path of Q 534.

On reaching the start up voltage the diode path becomes conductive and cuts the negative components. In these cases the E/W modulator diodes support this function, whereby in the switching transistor the power dissipation of the transistors is reduced

The horizontal deflection pulses are detached directly from the collector of the switching transistor on the parallel deflection winding. Between the base point of the horizontal deflector and the E/W diode modulator the east/west correction information is coupled in accordance with the dual generator principle. This procedure is almost non-reactive with respect to the primary winding of the high voltage transducer.

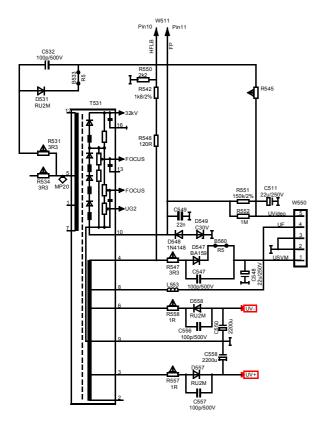

#### 2.4.1 High voltage production

#### Q2500 secondary H output stage

The high voltage transducer also contains the cascade. The secondary winding of the step up transformer is divided into four and the high voltage rectifier diodes are connected between the individual winding sections. This form of high voltage production is possible without the highly charged capacitors used up to now, which increases the reliability of high voltage production and makes possible a space-saving compact solution.

The resistance voltage divider and the potentiometer of the focus and G2 adjustment is integrated mechanically into the splitting combination for units with 4:3 c.r.t.s.

The filament voltage of the c.r.t. is assigned to pin 9. On pin 4 the flyback pulse for the syn-

chronisation of the control is assigned to pin 4. At the same time this pulse is rectified by D547 and fed to the c.r.t. plate via connector W 549. The 60V occurring here is required by the c.r.t. PCB for the speed modulator. The UV+ and UV- for the vertical stage (approx. ± 13 V) occur in the windings between pin 6 and 9 and pin 3 and 9.

Just like the amplitude of the radiation current a corrective voltage for the stabilisation of the horizontal amplitude can be tapped at the base, connection 10 of the high voltage winding.

This radiation current dependent voltage is led to the signal board via pin 11 of connector W 511. The radiation current fuse and limiter are found here.

The operating voltage U 200 for the video output stage is tapped on the primary side of the pin 5 of the diode split transformer and rectified by D 531. In addition on connection 5 another voltage UB -10 V and on pin 7 a voltage of UB +10 V are produced, which are felt on capacitors C 535 and C 534. On UB = 136 V there are 126 V and 146 V. These voltages are required for the offset correction of the horizontal deflector.

#### 2.4.2 Horizontal- offset deflector

The deflector pulse is formed in such a way that through the deflection and S-correction a linear deflection results. This only functions however when the deflection is exactly central. As the Q 2500 chassis could also be used as a VGA monitor, high demands are placed on linearity. For this reason the possibility of offset correction is created.

A free DAC in I 2271 is used for horizontal offset correction. The d.c. voltage felt on pin 55 can be set in the servicing mode. This is fed via connector W 511 /W 1511, pin 8, to the base of transistor Q 533 on the basic board. Q 533 together with R 555 represents a current source for the push-pull stage Q 531 and Q 532. The operating point for the push-pull stage is set with R 537 and the parallel circuit of R 535/538/539. At rest the operating voltage of the line output stage is applied to the base connections of Q 531/532 and both transistors are blocked.

If I 2271 increases the base voltage of transistor Q 533 and this then conducts, the base voltage of the push-pull stage drops and Q 531 conducts. This means the d.c. current is made more negative by resistors R 516, R 517 and R 518 and coil L 530, whereby the deflection shifts to the left.

If, on the other hand, the voltage on pin 27 of I 2271 drops, transistor Q 533 becomes high resistance and the base voltage on the pushpull stage increases. This means Q 532 conducts and L 530 increases the voltage on pin 2 of the deflection coil. This leads to a shifting of the d.c. current component in a positive direction and deflection to the right. Coil L 533 serves as d.c. current coupling for the deflection.

#### 2.5 East/west correction

In order to compensate for the pincushion (distortion) in 110° units in an east/west direction, the horizontal deflection current in the vertical centre must be increased with respect to the vertical start and vertical end. The right degree of correction is achieved by influencing the horizontal deflection current with a vertical frequency parabola in the east/west diode modulator.

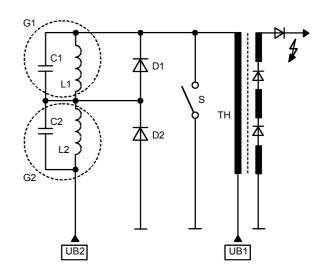

Two generators connected to each other by a bridging circuit provide the correction signal for the E/W modulator for the horizontal deflection current.

In the above drawing the two generators, G1 = horizontal generator, and G2 = east/west generator, are represented only by their resonant circuits. The deflection current in the deflection coil L1 is supplied by both generators. So that the high voltage is not influenced by the E/W modulator, the voltage on transformer TH is determined only by the horizontal generator G1. Therefore, for correct bridge compensation during the line trace, only E/W modulation of the deflection current takes place in an almost non-reactive fashion on the horizontal output level. For improved clarity the conceptual flow diagram above is shown in the following drawing with the actual component locations.

#### 2.5.1 Circuit

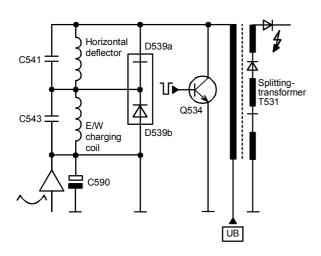

The components of the east/west output stage, as well as the diode modulator are located on the basic board.

# E/W correction W511 D334 D539 D5

The video/deflection processor TDA 9332 applies a d.c. underlying parabola type voltage to pin 3. This Information contains all corrections for picture width and east/west. The following amplifier stage, consisting of transistors Q 582 to Q 589, could therefore be implemented simply as a conventionally based differential amplifier.

Control is via low-pass filter R 581, C 581 and R 582 on the base of transistor Q 582. The low-pass filter suppresses any noise components from the pulse width generator in I 2521.

The base of transistor Q 589 is determined by the voltage divider R 588/R 589 in d.c. and thereby determines the operational point of the differential amplifier.

The amplification of the differential amplifier is determined essentially by the relationship of the negative feedback resistance R 583 and the output resistances R 581/582. The parabola type voltage, amplified to 12 V by output stages Q 585 and Q 586, is fed via the E/W charge coil to the diode modulator. Dual diode D 539 superimposes the deflection current on it and the E/W correction is implemented.

Transistor Q 593 was incorporated to protect the output stage transistor Q 586 in the event of the deflection connector being withdrawn. Normally Q 593 acts as positive feedback to Q 586. If the deflection connector is withdrawn the current increases through Q 586 and therefore also through resistors R 591 /R 592. This causes Q 593 to conduct and the power loss in Q 586 to be returned to a normal level. In the event of a fault the two transistors Q 596 and Q 597 ensure that the unit switches to protective operation. Q 596 is conductively controlled by a reduced base voltage. Q 597 conducts and controls VPROT at low level. The CCU protective circuit responds and switches the unit off.

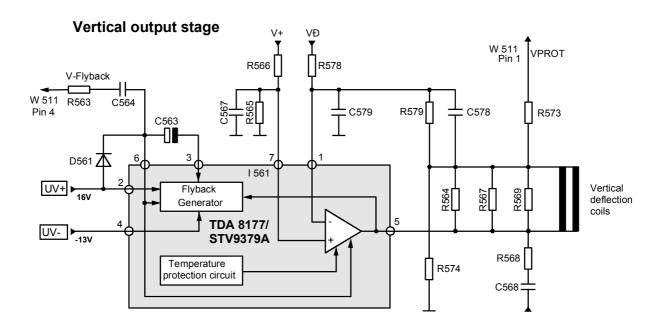

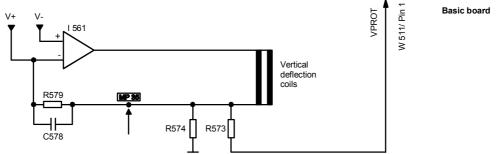

#### 2.6 Vertical output stage

In comparison with earlier models the Q 2500 generation of chassis does not have an a.c. coupled, but a d.c coupled vertical output stage. This has the advantage that the vertical deflection coils can be supplied with current directly and the large coupling capacitor can be dispensed with. This means that vertical correction information can operate directly, without vertical distortions caused by the deflection coil coupling capacitor.

As we know, a positive and a negative deflection current flow through the vertical deflection coils. In order for the d.c. coupled output stage to produce this negative current, it must be supplied with a +/- voltage.

The two possible variants of the vertical output stage IC's (TDA 8177/STV9379FA) incorporated into the 100 Hz Q 2500 chassis

are housed in a Heptawatt plastic housing.

The following functional groups are incorporated into the IC's as circuit components:

- A power operational amplifier that is able to drive the vertical deflection coils with a peak deflection current up to 3 Ass.

- A flyback generator, that generates the voltage charge for the vertical flyback.

- A temperature protection circuit that limits the deflection current on overload.

The power operational amplifier is controlled symmetrically and inversely on its non-inverting and inverting inputs. Therefore, the video/deflection processor outputs two inversely symmetrical vertical control signals.

#### Vertical output stage

These two control signals contain all vertical correction information. This means that output side S correction, which is necessary for a.c. coupled output stages, can be dispensed with completely. The component insert at the output of the V output stage is also considerably reduced. Symmetrical control almost fully suppresses interference that can affect the two V control signals due to the very high common mode rejection ratio of the V-power operating amplifier. The two V control signals V+/V- are applied to the pin connector W 511, pin 2/3 and reach the series resistors R 566 /R 578 via the inputs on pin 1/7 of the V output stage I 561. The sawtooth, which is amplified about 10 times, is output by pin 5 of I 561 and forces the current through the vertical deflection coils.

The R/C combination 568, from the output of pin 5 to earth, prevents the tendency of the output stage to oscillate and protects it from switching peaks that can be caused by the deflection coins. To stabilise the V output stage, part of the sawtooth from the base of the deflection coils is fed back via resistor R 579 to the inverted input pin 1.

Picture formation is normally established by the d.c. current component of the deflection current. This means that for a d.c. coupled V output stage, by simply changing the d.c. components of the control sawtooth, the d.c. component of the deflection current can be changed, and with it the picture formation.

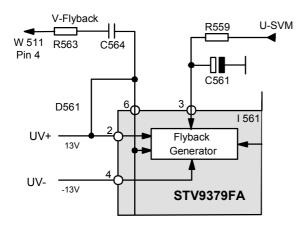

#### 2.6.1 Flyback generator

The job of the flyback generator is to provide, the switching voltage for the voltage increase during the vertical flyback. The problem with this is as follows:

The energy requirement of the vertical output stage is at its highest during the flyback, as the electron stream has to be directed rapidly from the lower right corner of the screen to the top left corner.

This transitory additional energy requirement is achieved by doubling the operating voltage, which is only available for the vertical output stage. During the vertical trace, the bootstrap capacitor C 563 is charged to approx. 26 V via D 561. The output of the flyback generator at pin 3 of I 561 at this point is UV-/-13 V. At the time of flyback start, the flyback generator is switched by the output stage output at pin 5 and applied to the output at pin 3 UV+/ +13 V. Due to the d.c. shift on the minus pin of capacitor C 563, the operating voltage for the output stage on pin 6 increases by the voltage in C 563. At the same time, D 561 is blocked, which prevents the charge in the power supply leaking away. This means that for rapid flyback there is a transitory +40 V (approx.) operating voltage available.

For many c.r.t. types the flyback pulse is not sufficient to fully return the deflection beam, so that flyback lines are visible.

In these devices the V output stage of STV9379FA is used. For the flyback generator this has an independent voltage supply. A USVM/60V is used that is fed to the I 561 via the fused resistor R 559 on pin 3.

If the V output stage is changed during service then ensure it is replaced with the same type. The two IC variants are not compatible.

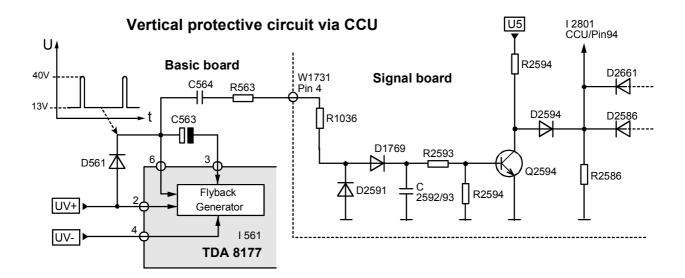

#### 2.6.2 Vertical protection circuits

Protection circuits are used to protect the c.r.t. against burning if the vertical deflection fails.

For a d.c. coupled V output stage a fault situation can theoretically occur in which the deflection saw tooth appears to be available, but a faulty d.c. component directs the electron beam to the upper or lower end of the c.r.t. neck. This could cause the c.r.t. neck to melt and lead to destruction of the c.r.t. neck.

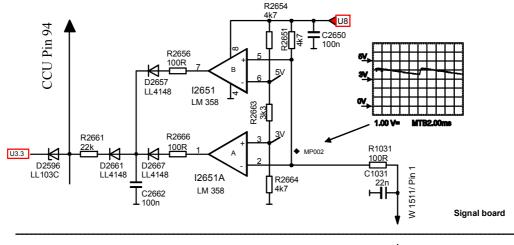

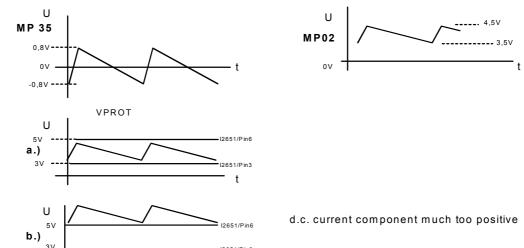

To prevent this a V saw tooth is taken from the base of the V deflection coils with R 573 and a d.c. voltage is applied to the signal board with R 2651.

This VPROT signal is fed to the protective circuit that consists of the dual operational amplifier I 2651. Operational amplifier A works on its non-inverting input pin 3, with reference voltage of 3 V and operational amplifier B on its inverting input pin 6 with 5 V. If the VPROT signal - Diagram A - does not fall below or exceed the reference values of 3V and 5 V, then the V deflection and the vertical d.c. component through the deflection coils is correct. If the d.c. component is too positive or

too negative - Diagrams B + C - this is interpreted as a fault. If, for example, the d.c. component of the VPROT signal is too small (<3V Diagram C), OP A controls its output on pin 1 to H level. This is fed, via the two D 2667/2661, to CCU pin 94. H level on pin 94 represents a fault and the CCU switches the device within about 2 secs to standby operation. If the d.c.level is too positive (>5V Diagram B) pin 7 goes from OP B to H level and the CCU switches the device off.

#### Vertical protective circuit via CCU

#### **Beam current limitation** D531 ┨╟ Signal board U8 12(9) 4 32kV BCI I 2521 **→** Uvid Video/deflection Processor R552 R551 R2611 R531 E/W amp. compensation Focus Phase compensation R2609 D548 D549 C2608 <del>H D</del>H UG2 R2608 C549 R1043 R2608 R2606 ┨├ R2544 R2547 D2544 W511/Pin11 T531 **Basic board** D2549 R2549 R2636 Q2638 U8

The second protective switch monitors the V flyback pulse that is fed from I 561 /pin 6 via R 563 to the pin connector W 511 /pin 4. On the signal board this V flyback pulse is rectified by diode D 2591/1769 and integrated with capacitor C 2592/2593. With the voltage available on capacitor C 2992/2593, Q 2594 conducts. The collector of Q 2594 is then at the same potential as L, and diode D 2594 is blocked.

If there is no flyback pulse due the absence of a V output stage, no voltage can build up on capacitors C 2592/2594 and Q 2594 blocks. Pin 94 of the CCU is set to H level via diode D 2594.

If pin 94 of C 161 is set to H level by the absence of a V flyback pulse in the operating condition of the unit, as described, after 2 seconds the CCU switches the device back to standby operation. This permits safe shut down of the device with a faulty deflection controller.

#### 2.7 Beam current limitation

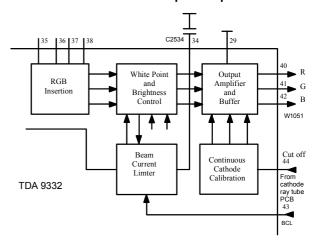

To limit the beam current the Q 2500 chassis is provided with an average value control. The limit switch is integrated into TDA 9332.

The switch to limit the contrast and brightness is controlled with a d.c value via pin 43.

The switch is designed in such a way that for a voltage of >3.3 V there is no limitation on contrast and brightness.

For a voltage between 3.3 and 2.2V the contrast is reduced in proportion to the voltage. If the voltage drops below 1.8 V the brightness as well as the contrast is reduced. At approx. 1 V on pin 15 the brightness and the contrast are reduced by 100%, whereupon the screen is black.

To achieve beam current limitation the base of the diode split transformer influences the d.c. value on pin 43 of TDA 9332. Inversely proportional voltage information on the beam current can be obtained at the base.

In order for the TDA pin to be at >3.3 V with a beam current of zero, the base of the transformer is connected to U 200 via R 551/552. The positive voltage in this operational state is

charged via resistors R 2608, R 2609 and R 2611 of Elko C 2603 and on pin 43 of the TDA there is a voltage of >3.3 V; there is no beam current limitation.

As the high voltage winding in the diode split transformer operates with a virtual earth, the base becomes negative with increasing beam current, whereby C 2603 via R 2608, R 2609 and R 2611 can be correspondingly discharged to a greater or lesser degree and the beam current controlled.

Diodes D 2607 and D 2611 are provided so that the circuit can also react to jumps in beam current. They ensure the rapid discharge of C 2603.

In addition, for a 4:3 display in a 16:9 TV set, from pin 113 of I 2311 via Q 2612 and R 2601, the voltage on C 2603 drops. This corrects the beam current limitation for the smaller screen area. (see also signal board deflection).

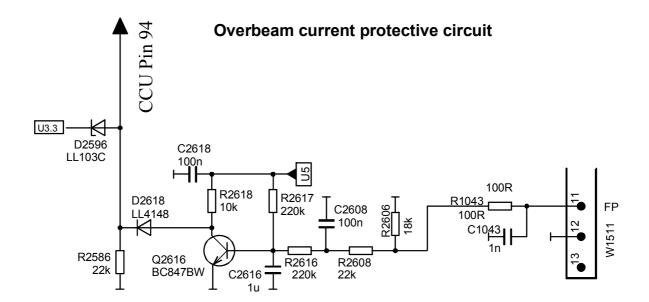

#### 2.7.1 Overbeam current fuse

In correct operation the beam current measurement input on pin 43 of TDA is at a d.c. level of 2 to 4 V. According to the level, the RGB output amplifier in this IC is controlled to

a greater or lesser extent, which ensures that the beam current limitation is implemented.

If the c.r.t. is controlled upwards to the full extent, even though the gain of the amplifier has been fully reduced, which can occur if there is a fault in the RGB output stage or its

power supply, then the c.r.t. could be damaged if no protective measures are taken.

To prevent this, transistor Q 2616 is connected to the beam current data. In normal operation the transistor conducts and L level is applied to its collector thus making the circuit inoperative.

If the described fault occurs, the base of the diode split transformer becomes negative due to the high beam current, Q 2616 blocks and due to the 5 V on its collector diode D 2618 conducts.

Pin 94 of the CCU is set to H level and switches the device to standby.

#### 2.7.2 HFLB protective circuit

If the line output stage is too strongly overloaded by a fault, the protective circuits discussed cannot respond in any way. Excessive overloading of the H output stage causes the line flyback pulse to reduce in amplitude. The HFLB pulse on pin 10 of W 1511 is therefore monitored by a protective circuit. In normal operation this pulse has an amplitude of approx. 35 V. Via the 20 V zener diode D 2581 this pulse makes Q 2581 conductive in rhythm with the line frequency. Capacitor C 2584 is switched to earth cyclically with the line frequency via Q 581 and cannot therefore charge up. This means that L level is felt on C 2584I. If a fault in the deflection circuit causes HFLB to fall below 20 V, zener diode D 2581 and Q 2581 block. C 2584 charges to H level. This H level is fed via D 2586 to pin 94 of the CCU, which switches the device back to standby operation.

#### 2.8 Speed modulator

The device is also equipped with a speed modulator. It is located between the RGB outputs of the digital unit and the RGB output stages on the c.r.t. board. It controls the speed of the electron beam in the horizontal direction, which increases picture sharpness and prevents a defocusing effect at high contrast on vertical, very bright areas of the picture.

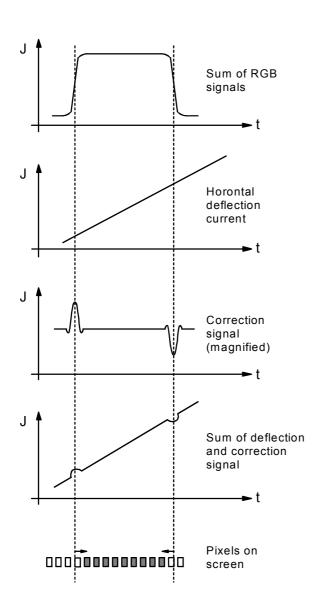

#### 2.8.1 General

The speed modulator evaluates high frequency changes in the picture signal and sends them to an additional winding in the deflector. The resulting magnetic field overlays the normal field produced by the deflection winding. By this method, the deflection speed is adapted to the picture content, which leads to a definite improvement in picture sharpness.

A picture change in a positive or negative direction produces a signal, as shown in the following drawing and thereby supplies the additional winding in the deflector.

The amplitude of the signal and the modulation level of the contrast are therefore dependent on the setting and the slope of the signal change.

One could also modulate the deflection current directly, which would however, be more expensive than the second winding.

To really understand the operation of the speed modulator we must look at the light characteristics of the pixels on the c.r.t. The longer a pixel is irradiated, the more intensively it shines, and the persistence of the fluorescent image is also longer.

If the signal jumps from dark to light, the deflection is initially accelerated briefly and thereafter remains mainly on one point. In this way the first "bright" pixel is irradiated for longer and therefore shines more brightly. At the same time the last "dark" pixel has more time to fade and is irradiated for a shorter time.

If the signal jumps from light to dark, however, this initially causes braking and then deceleration of the deflection in the speed modulator. This means the last "light" pixel is irradiated longer and therefore shines more brightly. On the other hand, the first "dark" pixel is irradiated for a shorter period.

In both cases another, simultaneous effect occurs. The signal change occurs while the electron beam, without almost any further deflection, remains on the last "bright" pixel.

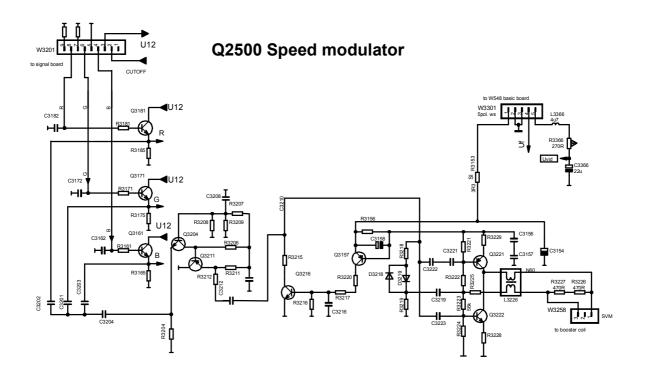

#### 2.8.2 Switching of the speed modulator

The circuit is located on the c.r.t. PCB and is supplied with RGB signals from TDA 9332 via pins 40/41/42.

The RGB signals are applied to connector W 3201 pins 4, 6, 8 at 3 Vss and are then fed via impedance converters Q 3181, Q 3171 and Q 3161. To detect changes in all three colours, the signals are decoupled by capacitors C 3201, C 3202 and C 3203 together. The resulting signal is differentiated with C 3204, R 3204. Control via the RGB signals offers the advantage that this circuit also works with Teletext and OSD operation.

This means that when steep signal changes occur there are only oscillation packages with max. 0.3 Vss on the emitter of transistor Q 3204 for processing.

The input for the circuit of transistor Q 3204 has a low resistance input, so that it can process steep slopes. From the collector the 4 Vss signals are led to the impedance converter Q 3211. This supplies the signal at 6 Vss to the push-pull output stage Q 3221 and Q 3222.

The two transistors are current counter coupled and amplify the signal to a maximum 50 Vss. All voltage data refers to a black/white change and maximum contrast.

Via the voltage dividers R 3221, R 3222, R 3223 and R 3224 one end of the correction coil on pin 1 of W 3258 is set to 30 V.

The two transistors Q 3221 and Q 3222 are blocked without control, so that the other end of the coil is hanging free and no current flows through the coil. Deflection occurs only via the horizontal deflection coil.

For a positive pulse transistor Q 3221 is blocked and Q 3222 conducts. This causes a current to flow via R 3221 and R 3222 through the booster coil and via Q 3222 to earth, which accelerates the deflection.

If, however, a negative pulse is felt, then Q 3221 conducts and Q 3222 is blocked. The

## Technology of Q 2500 colour TV set

current now flows via Q 3221 through the coil and then on via R 3223 and R 3224 to earth. The reversed direction of current causes the deflection to be arrested.

The deflection coil is controlled directly from the collector connections. Two resistors are connected in parallel to the deflection winding to stabilise the system and using L 3226 in the control lines a throttling of clock faults is achieved.

To prevent overshooting and overloading of the output stages a protective circuit is provided on the PCB. It affects the level of the input signal.

For very steep positive or negative flanks diodes D 3318 and D 319 conduct via C 3319. Positive flanks at the output reduce the input signal via D 3218, as the signal on the output is rotated by 180°. Negative flanks on the output reduce the input signal, as the input signals are directed to earth via D 3319. The circuit specification is such that it does not operate for small signal flanks, thereby ensuring secure operation of the speed modulator over a wide spectrum.

If there is no picture signal, but only noise, the output stages have become overheated. A protective circuit is therefore provided for this case as well.

If the current in the output stages increases, there is a larger voltage drop across current resistor R 3156. The base of Q 3157 goes negative and the transistor conducts. Elko C 3158 ensures that transient, but high currents for steep flanks are possible. Using transistor Q 3157 in conjunction with transistor Q 3216 the input signals of the output phase are reduced and overloading thereby prevented.

As there is a time difference of approx. 80 ns with respect to the RGB signals in the speed modulator circuit up to modulation of the deflection speed, the RGB signal circuit must be retarded by 80 ns after decoupling from the modulator if it is to function correctly. For this reason the 80 ns time lag lines, consisting, for example, of L 3392/3393, C 3392/3398/399 and R 3391/3393 are incorporated into the RGB lines.

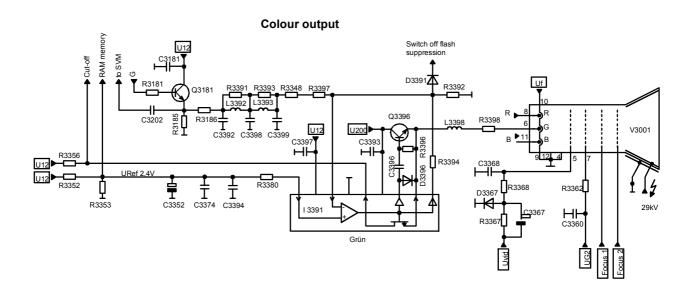

## 2.9 Colour stages

In order to avoid damaging capacitive charges caused by, for example, long cathode wires, which could lead to the frequency response being cut, the RGB output stages have been re-incorporated into the c.r.t. circuit board.

For each colour channel there is an IC whose signal bandwidth of >12 MHz guarantees a high resolution even for rapid signal changes in both directions.

The circuit for the three colour channels is identical. By using ICs the components in the output stages could be reduced to a minimum.

The output stages are energised by the speed modulator with a max. 3 Vss. Via an RC combination the respective signals reach pin 3 of the ICs and are passed on in the IC to the inverting input of an operational amplifier. The non-inverting input and thereby the work point is set via pin 1 of IC.

The resistance between pin 9 and pin 3 provides the negative feedback for determination of the amplification factor.

For control of the c.r.t. cathodes the signals are applied at a maximum 160 Vss via pin 7 and 8. Control is via pin 8 with a corrective signal on pin 7, in order to achieve an automatic blanking current control. The emitter follower on the output of the output stage permits rapid blocking of the cathodes on transition from bright to blank. This permits the delaying effects that are otherwise present to be reduced.

The IC's also contain a component for temperature drift compensation, as well as a circuit via which the transient current can be decoupled. Current information is taken from pin 5, and so with an additional sensor control circuit an automatic blanking value control (cut off control) can be established.

#### 2.9.1 Cut off control

The cut off control is basically a sensor control circuit. It controls electronically dynamic component tolerances and signs of wear, e.g. of the c.r.t.s.

It also has the following advantages:

- automatic blanking value equalisation.

- Avoidance of colour distortion during c.r.t. warm up time and control of above average ageing in the initial operating hours.

This means that the traditional adjustment controller and the associated adjustment work is no longer required.

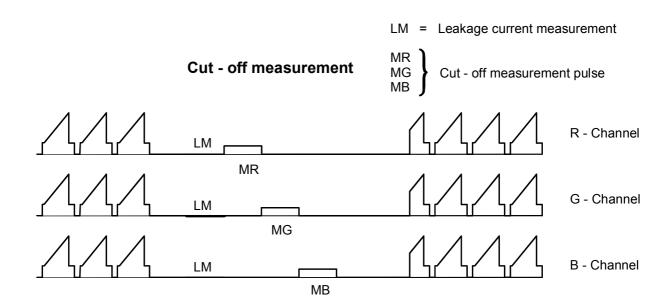

Directly after the vertical picture return, measurements are taken of the leakage current of the c.r.t. systems at ultra blank and then, one after the other, the cathode currents of the three systems after input of a specific blank value.

These pulses are fed with the respective RGB signals via the output stages of the c.r.t. systems. From the output stage IC's the respective blank currents of the control circuit in video IC I 2521 on the signal board are supplied via its pin 44.

From a comparison between the established blank current and a reference value, which represents the specified current, a difference is obtained, which controls the cathode current via the video output stages as a controller output. It is dynamically stabilised just above c.r.t. blocking current, up to control tolerances. As small leakage currents in the output stages of the c.r.t.s could lead to distortion of the cut

off control, measurement of the leakage current is carried out during the vertical flyback before measurement of the three blanking currents.

## Cut - off circuit principle

A consequence of a change to the UG2-voltage is that the cut off control opposes this change. Only a transient effect can be detected on the screen, as long as the control

range of the cut off control is not exceeded. This means an optical comparison of the raster 2 voltage is ruled out. A comparison using a voltmeter is also very unreliable, as the voltage source with approx. 500 MOhm is very resistive.

A comparison of the raster 2 voltage is therefore made in service mode.

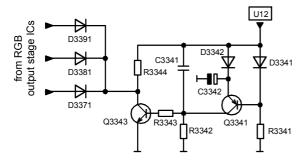

## 2.9.2 Switch off flash suppression

Transistors Q 3341 and 3343 are responsible for suppressing fluorescent flashes on switch off, caused by c.r.t. charges that are not discharged quickly enough via the bleeder in the DST. On start up and during operation they have no function, as the base and emitter of Q 3341 are at the same level it is therefore blocked, as is Q 3343.

On shut down the base of Q 3341 via R 3341 very quickly becomes zero volts. Due to Diode D 3342, that is blocked in the direction of the power supply, Elko C 3342 cannot discharge. Q 3341 switches through and that in C 3342 can switch through via the emitter-collector the output side connected transistor Q 3343. In this way the RGB signals that control the output stage IC's are directed to earth.

Fluorescent image persistence is thus avoided.

Until Elko C 3342 is discharged and the circuit becomes ineffective, the c.r.t. discharges via the bleeder.

## 2.10 Rotation panel

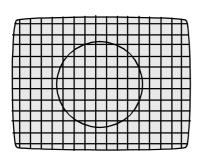

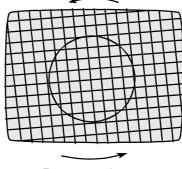

#### 2.10.1 Raster correction

So as the earth's magnetic field affects the colour uniformity of the c.r.t.s, it also influences the picture raster. For a geometrical comparison, a definite alignment towards east ("face to east") is therefore prescribed.

If the device is turned towards another point of the compass, rotation of the picture on the screen occurs according to the type and size of c.r.t. and local characteristics.

## Switch off flash suppression

#### **Raster correction**

"Face to East" comparison

Raster rotation

"Face to North"

Correction of raster rotation by rotation panel

To compensate for this a rotation panel (raster correction) is incorporated into the 81 cm device with chassis Q 2500. As the effect on the raster is less on smaller and 4:3 tubes the rotation panel is not required.

For the raster correction a circular coil is attached to the cone of the c.r.t. If a uniform current flows through it, the electron beam rotates around its own axis. As the created magnetic field overlays the field of the deflection coils, the picture can be rotated about its central point.

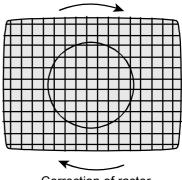

#### 2.10.2 Circuit

For raster correction the DAC on pin 25 of the video/deflection processor TDA 9332 is used. The voltage produced can be adjusted by the user via "rotate picture" and in service mode. It flows via W 1021, pin 3 to the rotation panel W 1, pin 3.

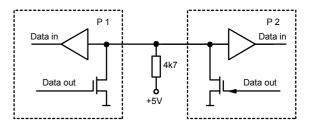

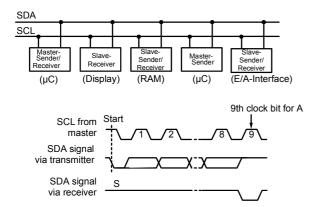

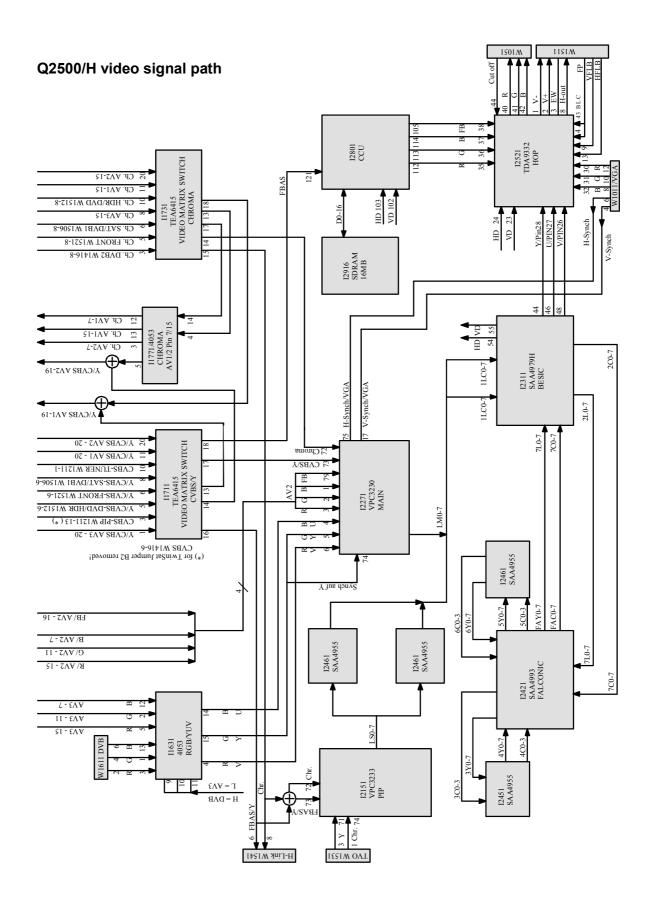

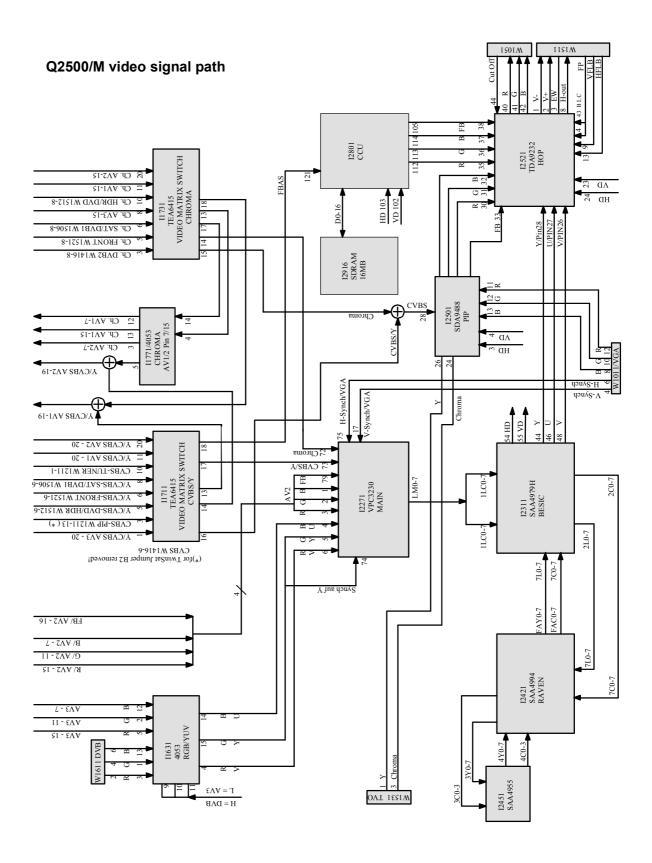

In this way the inverting input of the operational amplifier on pin 9 of I1C is controlled on the rotation panel. At maximum anticlockwise rotation approximately 3.2 V is applied and at maximum clockwise rotation 3.3 V. The operational point is adjusted on pin 10 by R21 and R23. According to the voltage difference between pin 10 and pin 9 the push-pull stage Q26 and Q28 is controlled. On the base connections there is a voltage of 0.6 to 10.6 V. The output voltage of the push-pull stage is applied to pin 2 of the correction coil and at the same time is fed to the inverting input of operational amplifier I1A via R 38 and R41. This also controls the second push-pull stage Q 48/Q 47. The two OPVs and push-pull stages counteract each other. This means that a current can flow to earth via Q 26, through the correction coil (from pin 2 to pin 1 on W31) and via Q48. On pin 8 of the OPV there is a voltage of 10.6V at maximum clockwise rotation and on the other output pin 1, 0.6 V. Otherwise the current flows via Q 47 through the correction coil (in this case from pin 1 to pin 2 on W 31) and via Q28 to earth.