www.ti.com

SBFS036A - AUGUST 2011-REVISED JULY 2012

# Stereo Audio DAC with USB Interface, Single-Ended Headphone Output and S/PDIF Output

Check for Samples: PCM2704C, PCM2705C, PCM2706C, PCM2707C

## **FEATURES**

- On-Chip USB Interface:

- No Dedicated Device Driver Needed

- Full-Speed Transceivers

- Fully Compliant with USB 2.0 Specification

- USB 1.1 Descriptors with USB Audio Class Support

- Certified by USB-IF

- Partially Programmable Descriptors

- Adaptive Isochronous Transfer for **Playback**

- Bus-Powered or Self-Powered Operation

- Sampling Rates: 32 kHz, 44.1 kHz, 48 kHz

- **On-Chip Clock Generator with Single 12-MHz Clock Source**

- **Single Power Supply:**

- Bus-Powered: 5 V, Typical (V<sub>BUS</sub>)

- Self-Powered: 3.3 V, Typical

- 16-Bit Delta-Sigma Stereo DAC

- Analog Performance at 5 V (Bus-Powered), 3.3 V (Self-Powered):

- THD+N: 0.006%  $R_L > 10 kΩ$ , Self-**Powered**

- THD+N: 0.025%  $R_1$  = 32 Ω

- SNR = 98 dB

- Dynamic Range: 98 dB

- P<sub>O</sub> = 12 mW, R<sub>L</sub> = 32 Ω

- Oversampling Digital Filter

- Stop-Band Attenuation = -50 dB

Passband Ripple = ±0.04 dB

- Single-Ended Voltage Output

- Analog LPF Included

- **Multiple Functions:**

- **Up to Eight Human Interface Device (HID)** Interfaces (Model and Setting Dependent)

- Suspend Flag

- S/PDIF Out with SCMS

- External ROM Interface (PCM2704C/6C)

- Serial Programming Interface (PCM2705C/7C)

- I<sup>2</sup>S™ Interface (Selectable on PCM2706C/7C)

- Packages:

- 28-Pin SSOP (PCM2704C/5C)

- 32-Pin TQFP (PCM2706C/7C)

## APPLICATIONS

- **USB Headphones**

- **USB Audio Speaker**

- **USB CRT/LCD Monitor**

- **USB Audio Interface Box**

- **USB-Featured Consumer Audio Product**

#### DESCRIPTION

The PCM2704C/5C/6C/7C are TI's single-chip USB stereo audio digital-to-analog converters (DACs) with USB 2.0 compliant full-speed protocol controller and S/PDIF. The USB-protocol controller works with no software code, but USB descriptors can be modified in some areas (for example, vendor ID/product ID) through the use of an external ROM (PCM2704C/6C) or serial peripheral interface (SPI) (PCM2705C/7C). The PCM2704C/5C/6C/7C also employ SpAct™ architecture, TI's unique system that recovers the audio clock from USB packet data. On-chip analog phase-locked loops (PLLs) with SpAct enable playback with low clock jitter.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SpAct is a trademark of Texas Instruments.

System Two, Audio Precision are trademarks of Audio Precision, Inc.

SPI is a trademark of Motorola, Inc.

I<sup>2</sup>S, I<sup>2</sup>C are trademarks of NXP Semiconductors. All other trademarks are the property of their respective owners.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

## **ORDERING INFORMATION**

For the most current specification and package information, refer to the Package Option Addendum located at the end of this data sheet or see the respective device product folders at www.ti.com.

## **ABSOLUTE MAXIMUM RATINGS(1)**

Over operating free-air temperature range unless otherwise noted.

|                                          |                                                                                                                              | VALUE                               | UNIT |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|------|

| Cupply voltage                           | V <sub>BUS</sub>                                                                                                             | -0.3 to 6.5                         | V    |

| Supply voltage                           | V <sub>CCP</sub> , V <sub>CCL</sub> , V <sub>CCR</sub> , V <sub>DD</sub>                                                     | -0.3 to 4                           | V    |

| Supply voltage differences               | V <sub>CCP</sub> , V <sub>CCL</sub> , V <sub>CCR</sub> , V <sub>DD</sub>                                                     | ±0.1                                | V    |

| Ground voltage differences               | PGND, AGNDL, AGNDR, DGND, ZGND                                                                                               | ±0.1                                | V    |

|                                          | HOST                                                                                                                         | -0.3 to 6.5                         | V    |

| Digital input voltage                    | D+, D-, HID0/MS, HID1/MC, HID2/MD, XTI, XTO, DOUT, SSPND, CK, DT, PSEL, FSEL, TEST, TEST0, TEST1, FUNC0, FUNC1, FUNC2, FUNC3 | -0.3 to (V <sub>DD</sub> + 0.3) < 4 | V    |

|                                          | V <sub>COM</sub>                                                                                                             | $-0.3$ to $(V_{CCP} + 0.3) < 4$     | V    |

| Analog input voltage                     | V <sub>OUT</sub> R                                                                                                           | $-0.3$ to $(V_{CCR} + 0.3) < 4$     | V    |

|                                          | V <sub>OUT</sub> L                                                                                                           | $-0.3$ to $(V_{CCL} + 0.3) < 4$     | V    |

| Input current (any pins except supplies) |                                                                                                                              | ±10                                 | mA   |

| Ambient temperature under bias           |                                                                                                                              | -40 to +125                         | °C   |

| Storage temperature                      |                                                                                                                              | -55 to +150                         | °C   |

| Junction temperature                     |                                                                                                                              | +150                                | °C   |

| Package temperature (IR ref              | low, peak)                                                                                                                   | +260                                | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## RECOMMENDED OPERATING CONDITIONS

Over operating free-air temperature range.

|                                                |                                     | MIN    | NOM         | MAX    | UNIT |

|------------------------------------------------|-------------------------------------|--------|-------------|--------|------|

| Cumply voltage                                 | V <sub>BUS</sub>                    | 4.35   | 5           | 5.25   | V    |

| Supply voltage                                 | $V_{CCP}, V_{CCL}, V_{CCR}, V_{DD}$ | 3      | 3.3         | 3.6    | V    |

| Digital input logic level                      |                                     | TTL    | -compatible |        |      |

| Digital input clock frequency                  |                                     | 11.994 | 12          | 12.006 | MHz  |

| Analog output load resistance                  |                                     | 16     | 32          |        | Ω    |

| Analog output load capacitance                 |                                     |        |             | 100    | pF   |

| Digital output load capacitance                |                                     |        | 20          | pF     |      |

| Operating free-air temperature, T <sub>A</sub> |                                     | -25    |             | 85     | °C   |

#### **ELECTRICAL CHARACTERISTICS**

All specifications at  $T_A = +25$ °C,  $V_{BUS} = 5$  V,  $f_S = 44.1$  kHz,  $f_{IN} = 1$  kHz, and 16-bit data (unless otherwise noted).

|                     | PARAMETER                              |               | TEST CONDITIONS                                                     | PCM2704CI<br>PCM2706CP |                |           | UNIT     |  |

|---------------------|----------------------------------------|---------------|---------------------------------------------------------------------|------------------------|----------------|-----------|----------|--|

|                     |                                        |               |                                                                     | MIN                    | TYP            | MAX       |          |  |

| DIGITAI             | L INPUT/OUTPUT                         |               | ·                                                                   | •                      |                | •         |          |  |

|                     | Host interface                         |               |                                                                     | Apply USB re           | vision 1.1, fu | ıll-speed |          |  |

|                     | Audio data format                      |               |                                                                     | USB isochr             | onous data t   | format    |          |  |

| INPUT L             | OGIC                                   |               | -                                                                   |                        |                |           |          |  |

| $V_{IH}$            |                                        |               |                                                                     | 2                      |                | 3.3       |          |  |

| $V_{IL}$            | Input logic level                      |               |                                                                     | -0.3                   |                | 0.8       | $V_{DC}$ |  |

| $V_{IH}^{(1)}$      | Input logic level                      |               |                                                                     | 2                      |                | 5.5       | v DC     |  |

| $V_{IL}^{(1)}$      |                                        |               |                                                                     | -0.3                   |                | 0.8       |          |  |

| I <sub>IH</sub> (2) |                                        |               | $V_{IN} = 3.3 V$                                                    |                        |                | ±10       |          |  |

| I <sub>IL</sub> (2) | Input logic current                    |               | $V_{IN} = 0 V$                                                      |                        |                | ±10       |          |  |

| I <sub>IH</sub>     | Input logic current                    |               | $V_{IN} = 3.3 V$                                                    |                        | 65             | 100       | μA       |  |

| I <sub>IL</sub>     |                                        |               | $V_{IN} = 0 V$                                                      |                        |                | ±10       |          |  |

| OUTPU               | T LOGIC                                |               |                                                                     |                        |                |           |          |  |

| V <sub>OH</sub> (3) |                                        |               | $I_{OH} = -2 \text{ mA}$                                            | 2.8                    |                |           |          |  |

| V <sub>OL</sub> (3) | Outrout le sie level                   |               | I <sub>OL</sub> = 2 mA                                              |                        |                | 0.3       | $V_{DC}$ |  |

| V <sub>OH</sub>     | Output logic level                     |               | $I_{OH} = -2 \text{ mA}$                                            | 2.4                    |                |           |          |  |

| V <sub>OL</sub>     |                                        |               | I <sub>OL</sub> = 2 mA                                              |                        |                | 0.4       |          |  |

| CLOCK               | FREQUENCY                              |               |                                                                     |                        |                |           |          |  |

|                     | Input clock frequency,                 | XTI           |                                                                     | 11.994                 | 12             | 12.006    | MHz      |  |

| $f_S$               | Sampling frequency                     |               |                                                                     | 32                     | , 44.1, 48     |           | kHz      |  |

| DAC CH              | <b>HARACTERISTICS</b>                  |               |                                                                     | •                      |                | •         |          |  |

|                     | Resolution                             |               |                                                                     |                        | 16             |           | Bits     |  |

|                     | Audio data channel                     |               |                                                                     |                        | 1, 2           |           | Channel  |  |

| DC ACC              | CURACY                                 |               |                                                                     |                        |                |           |          |  |

|                     | Gain mismatch, chann                   | el-to-channel |                                                                     |                        | ±2             | ±8        | % of FSR |  |

|                     | Gain error                             |               |                                                                     |                        | ±2             | ±8        | % of FSR |  |

|                     | Bipolar zero error                     |               |                                                                     |                        | ±3             | ±6        | % of FSR |  |

| DYNAM               | IC PERFORMANCE (4)                     |               |                                                                     |                        |                |           |          |  |

|                     |                                        | Line (5)      | $R_L > 10 \text{ k}\Omega$ , self-powered, $V_{OUT} = 0 \text{ dB}$ |                        | 0.006          | 0.01      | %        |  |

| THD+N               | HD+N Total harmonic distortion + noise | Line (-/      | $R_L > 10 \text{ k}\Omega$ , bus-powered, $V_{OUT} = 0 \text{ dB}$  |                        | 0.012          | 0.02      | %        |  |

|                     |                                        | Headphone     | $R_L = 32 \Omega$ , self-/<br>bus-powered, $V_{OUT} = 0 dB$         |                        | 0.025          |           | %        |  |

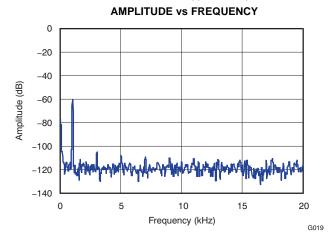

| THD+N               | Total harmonic distortion              | on + noise    | $V_{OUT} = -60 \text{ dB}$                                          |                        | 2              |           | %        |  |

|                     | Dynamic range                          |               | EIAJ, A-weighted                                                    | 90                     | 98             | -         | dB       |  |

| SNR                 | Signal-to-noise ratio                  |               | EIAJ, A-weighted                                                    | 90                     | 98             |           | dB       |  |

|                     | Channel separation                     |               |                                                                     | 60                     | 70             |           | dB       |  |

<sup>(1)</sup> HOST pin.

D+, D-, HOST, TEST, TEST0, TEST1, DT, PSEL, FSEL, XTI pins. FUNC0, FUNC1, FUNC2 pins.

f<sub>IN</sub> = 1 kHz, using the System Two™ Cascade audio measurement system by Audio Precision™ in RMS mode with a 20-kHz low-pass filter (LPF) and 400-Hz high-pass filter (HPF).

THD+N performance varies slightly, depending on the effective output load, including dummy load R7, R8 in Figure 34.

# **ELECTRICAL CHARACTERISTICS (continued)**

All specifications at  $T_A = +25$ °C,  $V_{BUS} = 5$  V,  $f_S = 44.1$  kHz,  $f_{IN} = 1$  kHz, and 16-bit data (unless otherwise noted).

| PARAMET                           | ER                                                                       | TEST CONDITIONS                     | PCM2704CDB, PCM2705CDB<br>PCM2706CPJT, PCM2707CPJT |                                       |                      | UNIT         |

|-----------------------------------|--------------------------------------------------------------------------|-------------------------------------|----------------------------------------------------|---------------------------------------|----------------------|--------------|

|                                   |                                                                          |                                     | MIN                                                | TYP                                   | MAX                  |              |

| NALOG OUTPUT                      |                                                                          |                                     | •                                                  |                                       | *                    |              |

| Output voltage                    |                                                                          |                                     | 0.55 V <sub>C</sub>                                | <sub>CCL</sub> , 0.55 V <sub>CC</sub> | CR                   | $V_{PP}$     |

| Center voltage                    |                                                                          |                                     | 0                                                  | .5 V <sub>CCP</sub>                   |                      | V            |

| Load impadance                    | Line                                                                     | AC-coupling                         | 10                                                 |                                       |                      | kΩ           |

| Load impedance                    | Headphone                                                                | AC-coupling                         | 16                                                 | 32                                    |                      | Ω            |

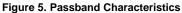

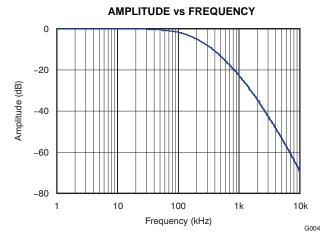

| LDE fraguency roopen              | •                                                                        | -3 dB                               |                                                    | 140                                   |                      | kHz          |

| LPF frequency respon-             | Se                                                                       | f = 20 kHz                          |                                                    | -0.1                                  |                      | dB           |

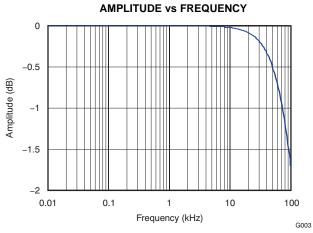

| IGITAL FILTER PERFORMAN           | ICE                                                                      |                                     |                                                    |                                       |                      |              |

| Passband                          |                                                                          |                                     |                                                    |                                       | 0.454 f <sub>S</sub> | Hz           |

| Stop band                         |                                                                          |                                     | 0.546 f <sub>S</sub>                               |                                       |                      | Hz           |

| Passband ripple                   |                                                                          |                                     |                                                    |                                       | ±0.04                | dB           |

| Stop band attenuation             | Stop band attenuation                                                    |                                     | -50                                                |                                       |                      | dB           |

| Delay time                        |                                                                          |                                     |                                                    | 20/f <sub>S</sub>                     |                      | s            |

| OWER SUPPLY REQUIREME             | NTS                                                                      |                                     |                                                    |                                       |                      |              |

|                                   | V <sub>BUS</sub>                                                         | Bus-powered                         | 4.35                                               | 5                                     | 5.25                 | $V_{DC}$     |

| Voltage range                     | $V_{CCP}, V_{CCL}, V_{CCR}, V_{DD}$                                      | Self-powered                        | 3                                                  | 3.3                                   | 3.6                  |              |

|                                   | Line                                                                     | DAC operation                       |                                                    | 23                                    | 30                   | mA           |

| Supply current                    | Headphone                                                                | DAC operation ( $R_L = 32 \Omega$ ) |                                                    | 35                                    | 46                   |              |

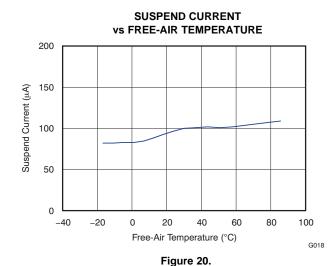

|                                   | Line/headphone                                                           | Suspend mode (6)                    |                                                    | 150                                   | 190                  | μΑ           |

|                                   | Line                                                                     | DAC operation                       |                                                    | 76                                    | 108                  | mW           |

| Power dissipation (self-powered)  | Headphone                                                                | DAC operation ( $R_L = 32 \Omega$ ) |                                                    | 116                                   | 166                  |              |

| (Scii powerca)                    | Line/headphone                                                           | Suspend mode (6)                    |                                                    | 495                                   | 684                  | μW           |

| _                                 | Line                                                                     | DAC operation                       |                                                    | 115                                   | 158                  | <b>\ A</b> / |

| Power dissipation (bus-powered)   | Headphone                                                                | DAC operation ( $R_L = 32 \Omega$ ) |                                                    | 175                                   | 242                  | mW           |

| (bus-powereu)                     | Line/headphone                                                           | Suspend mode (6)                    |                                                    | 750                                   | 998                  | μW           |

| Internal power-supply voltage (7) | V <sub>CCP</sub> , V <sub>CCL</sub> , V <sub>CCR</sub> , V <sub>DD</sub> | Bus-powered                         | 3.2                                                | 3.35                                  | 3.5                  | $V_{DC}$     |

| EMPERATURE RANGE                  | •                                                                        |                                     |                                                    |                                       |                      |              |

| Operating temperature             | }                                                                        |                                     | -25                                                |                                       | +85                  | °C           |

<sup>(6)</sup> In USB suspended state.

<sup>(7)</sup> V<sub>DD</sub>, V<sub>CCP</sub>, V<sub>CCL</sub>, V<sub>CCR</sub> pins. These pins work as output pins of internal power supply for bus-powered operation.

## THERMAL INFORMATION

|                  | <i>(</i> 0)                                  | PCM2704C,<br>PCM2705C |       |

|------------------|----------------------------------------------|-----------------------|-------|

|                  | THERMAL METRIC <sup>(1)</sup>                | DB                    | UNITS |

|                  |                                              | 32 PINS               |       |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance       | 68.2                  |       |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance    | 27.2                  |       |

| $\theta_{JB}$    | Junction-to-board thermal resistance         | 29.5                  | °C/W  |

| ΨЈТ              | Junction-to-top characterization parameter   | 2.7                   | C/VV  |

| ΨЈВ              | Junction-to-board characterization parameter | 29.1                  |       |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance | N/A                   |       |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

## THERMAL INFORMATION

|                  | 40                                           | PCM2706C,<br>PCM2707C |       |

|------------------|----------------------------------------------|-----------------------|-------|

|                  | THERMAL METRIC <sup>(1)</sup>                | PJT                   | UNITS |

|                  |                                              | 32 PINS               |       |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance       | TBD                   |       |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance    | TBD                   |       |

| $\theta_{JB}$    | Junction-to-board thermal resistance         | TBD                   | °C/W  |

| ΨЈТ              | Junction-to-top characterization parameter   | TBD                   | *C/VV |

| ΨЈВ              | Junction-to-board characterization parameter | TBD                   |       |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance | TBD                   |       |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

#### **DEVICE INFORMATION**

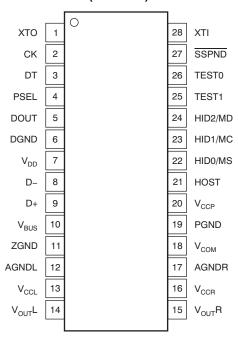

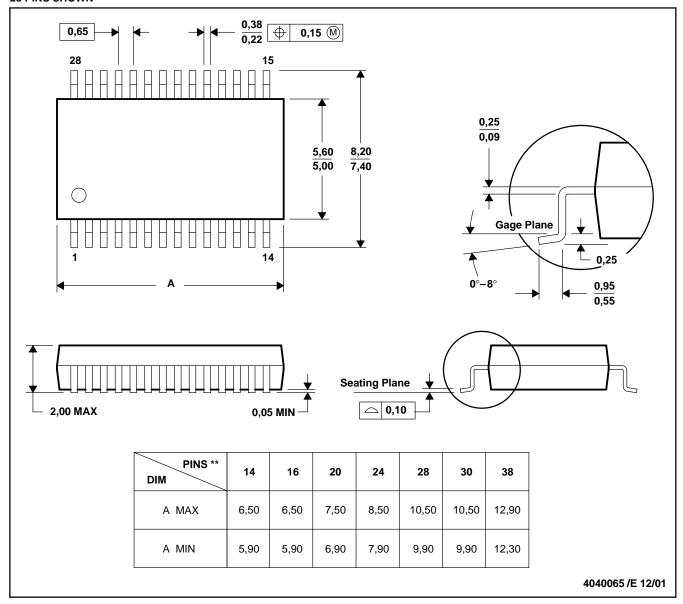

#### PCM2704C, PCM2705C DB PACKAGE (TOP VIEW)

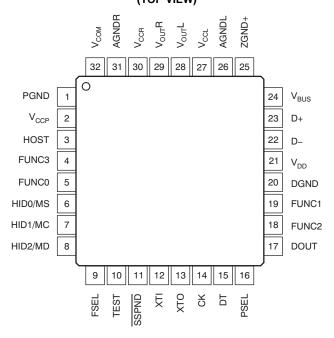

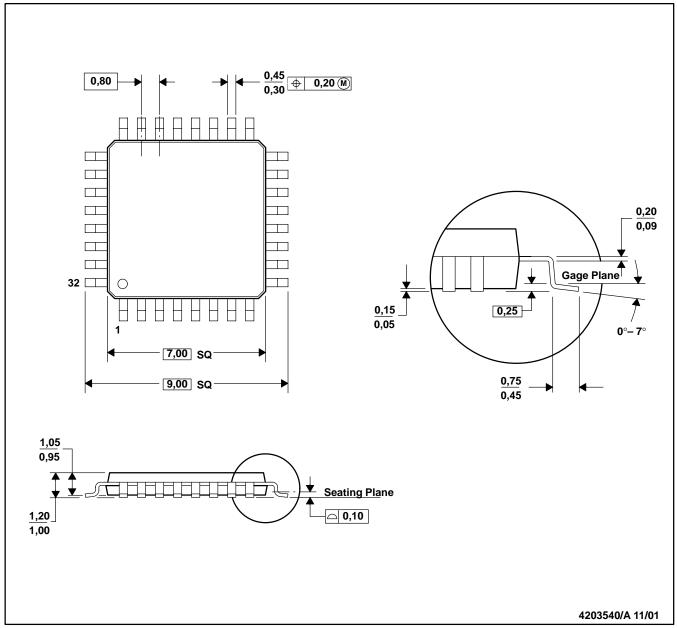

#### PCM2706C, PCM2707C PJT PACKAGE (TOP VIEW)

# Table 1. Pin Descriptions: DB Package (PCM2704C/PCM2705C)

| TERMIN             | AL  |            |                                                                                                                                                             |

|--------------------|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME               | NO. | I/O        | DESCRIPTION                                                                                                                                                 |

| AGNDL              | 12  | _          | Analog ground for headphone amplifier of L-channel                                                                                                          |

| AGNDR              | 17  | _          | Analog ground for headphone amplifier of R-channel                                                                                                          |

| CK                 | 2   | 0          | Clock output for external ROM (PCM2704C). Must be left open (PCM2705C).                                                                                     |

| D+                 | 9   | I/O        | USB differential input/output plus <sup>(1)</sup>                                                                                                           |

| D-                 | 8   | I/O        | USB differential input/output minus <sup>(1)</sup>                                                                                                          |

| DGND               | 6   | -          | Digital ground                                                                                                                                              |

| DOUT               | 5   | 0          | S/PDIF output                                                                                                                                               |

| DT                 | 3   | I/O        | Data input/output for external ROM (PCM2704C). Must be left open with pull-up resistor (PCM2705C). (1)                                                      |

| HID0/MS            | 22  | - 1        | HID key state input (mute), active high (PCM2704C). MS input (PCM2705C). (2)                                                                                |

| HID1/MC            | 23  | - 1        | HID key state input (volume up), active high (PCM2704C). MC input (PCM2705C). (2)                                                                           |

| HID2/MD            | 24  | ı          | HID key state input (volume down), active high (PCM2704C). MD input (PCM2705C). (2)                                                                         |

| HOST               | 21  | 1          | Host detection during self-powered operation (connect to V <sub>BUS</sub> ). Max power select during bus-powered operation (low: 100 mA, high: 500 mA). (3) |

| PGND               | 19  | _          | Analog ground for DAC, OSC, and PLL                                                                                                                         |

| PSEL               | 4   | I          | Power source select (low: self-power, high: bus-power) <sup>(1)</sup>                                                                                       |

| SSPND              | 27  | 0          | Suspend flag, active low (low: suspend, high: operational)                                                                                                  |

| TEST0              | 26  | - 1        | Test pin. Must be set high (1)                                                                                                                              |

| TEST1              | 25  | - 1        | Test pin. Must be set high <sup>(1)</sup>                                                                                                                   |

| V <sub>BUS</sub>   | 10  | _          | Connect to USB power ( $V_{BUS}$ ) for bus-powered operation. Connect to $V_{DD}$ for self-powered operation.                                               |

| V <sub>CCL</sub>   | 13  |            | Analog power supply for headphone amplifier of L-channel <sup>(4)</sup>                                                                                     |

| $V_{CCP}$          | 20  | _          | Analog power supply for DAC, OSC, and PLL <sup>(4)</sup>                                                                                                    |

| V <sub>CCR</sub>   | 16  | _          | Analog power supply for headphone amplifier of R-channel (4)                                                                                                |

| V <sub>COM</sub>   | 18  | <u> </u> — | Common voltage for DAC (V <sub>CCP</sub> /2). Connect decoupling capacitor to PGND.                                                                         |

| $V_{DD}$           | 7   | -          | Digital power supply <sup>(4)</sup>                                                                                                                         |

| V <sub>OUT</sub> L | 14  | 0          | DAC analog output for L-channel                                                                                                                             |

| V <sub>OUT</sub> R | 15  | 0          | DAC analog output for R-channel                                                                                                                             |

| XTI                | 28  | 1          | Crystal oscillator input <sup>(1)</sup>                                                                                                                     |

| XTO                | 1   | 0          | Crystal oscillator output                                                                                                                                   |

| ZGND               | 11  | -          | Ground for internal regulator                                                                                                                               |

LV-TTL level.

LV-TTL level with internal pulldown.

LV-TTL level, 5-V tolerant.

Connect decoupling capacitor to GND. Supply 3.3 V for self-powered applications.

# Table 2. Pin Descriptions: PJT Package (PCM2706C/PCM2707C)

| TERMIN             | AL  |     |                                                                                                                                                              |

|--------------------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME               | NO. | 1/0 | DESCRIPTION                                                                                                                                                  |

| AGNDL              | 26  | _   | Analog ground for headphone amplifier of L-channel                                                                                                           |

| AGNDR              | 31  | _   | Analog ground for headphone amplifier of R-channel                                                                                                           |

| CK                 | 14  | 0   | Clock output for external ROM (PCM2706C). Must be left open (PCM2707C).                                                                                      |

| D+                 | 23  | I/O | USB differential input/output plus <sup>(1)</sup>                                                                                                            |

| D-                 | 22  | I/O | USB differential input/output minus <sup>(1)</sup>                                                                                                           |

| DGND               | 20  | _   | Digital ground                                                                                                                                               |

| DOUT               | 17  | 0   | S/PDIF output/I <sup>2</sup> S data output                                                                                                                   |

| DT                 | 15  | I/O | Data input/output for external ROM (PCM2706C). Must be left open with pull-up resistor (PCM2707C). (1)                                                       |

| FSEL               | 9   | I   | Function select (low: I <sup>2</sup> S data output, high: S/PDIF output) <sup>(1)</sup>                                                                      |

| FUNC0              | 5   | I/O | HID key state input (next track), active high (FSEL = 1). I <sup>2</sup> S LR clock output (FSEL = 0). (2)                                                   |

| FUNC1              | 19  | I/O | HID key state input (previous track), active high (FSEL = 1). I <sup>2</sup> S bit clock output (FSEL = 0). (2)                                              |

| FUNC2              | 18  | I/O | HID key state input (stop), active high (FSEL = 1). I <sup>2</sup> S system clock output (FSEL = 0). (2)                                                     |

| FUNC3              | 4   | Į   | HID key state input (play/pause), active high (FSEL = 1). I <sup>2</sup> S data input (FSEL = 0). (2)                                                        |

| HID0/MS            | 6   | Į   | HID key state input (mute), active high (PCM2706C). MS input (PCM2707C). (2)                                                                                 |

| HID1/MC            | 7   | ı   | HID key state input (volume up), active high (PCM2706C). MC input (PCM2707C). (2)                                                                            |

| HID2/MD            | 8   | ı   | HID key state input (volume down), active high (PCM2706C). MD input (PCM2707C). (2)                                                                          |

| HOST               | 3   | ı   | Host detection during self-powered operation (connect to V <sub>BUS</sub> ). Max power select during bus-powered operation. (low: 100 mA, high: 500 mA). (3) |

| PGND               | 1   | _   | Analog ground for DAC, OSC, and PLL                                                                                                                          |

| PSEL               | 16  | ı   | Power source select (low: self-power, high: bus-power) <sup>(1)</sup>                                                                                        |

| SSPND              | 11  | 0   | Suspend flag, active low (low: suspend, high: operational)                                                                                                   |

| TEST               | 10  | 1   | Test pin. Must be set high <sup>(1)</sup>                                                                                                                    |

| V <sub>BUS</sub>   | 24  | _   | Connect to USB power ( $V_{BUS}$ ) for bus-powered operation. Connect to $V_{DD}$ for self-powered operation.                                                |

| V <sub>CCL</sub>   | 27  | _   | Analog power supply for headphone amplifier of L-channel <sup>(4)</sup>                                                                                      |

| V <sub>CCP</sub>   | 2   | _   | Analog power supply for DAC, OSC, and PLL <sup>(4)</sup>                                                                                                     |

| V <sub>CCR</sub>   | 30  | _   | Analog power supply for headphone amplifier of R-channel (4)                                                                                                 |

| V <sub>СОМ</sub>   | 32  | _   | Common voltage for DAC (V <sub>CCP</sub> /2). Connect decoupling capacitor to PGND.                                                                          |

| $V_{DD}$           | 21  |     | Digital power supply <sup>(4)</sup>                                                                                                                          |

| √ <sub>OUT</sub> L | 28  | 0   | DAC analog output for L-channel                                                                                                                              |

| √ <sub>OUT</sub> R | 29  | 0   | DAC analog output for R-channel                                                                                                                              |

| XTI                | 12  | I   | Crystal oscillator input <sup>(1)</sup>                                                                                                                      |

| ХТО                | 13  | 0   | Crystal oscillator output                                                                                                                                    |

| ZGND               | 25  | _   | Ground for internal regulator                                                                                                                                |

- (1) LV-TTL level.

- (2) LV-TTL level with internal pulldown.

- (3) LV-TTL level, 5-V tolerant.

- (4) Connect decoupling capacitor to GND. Supply 3.3 V for self-powered applications.

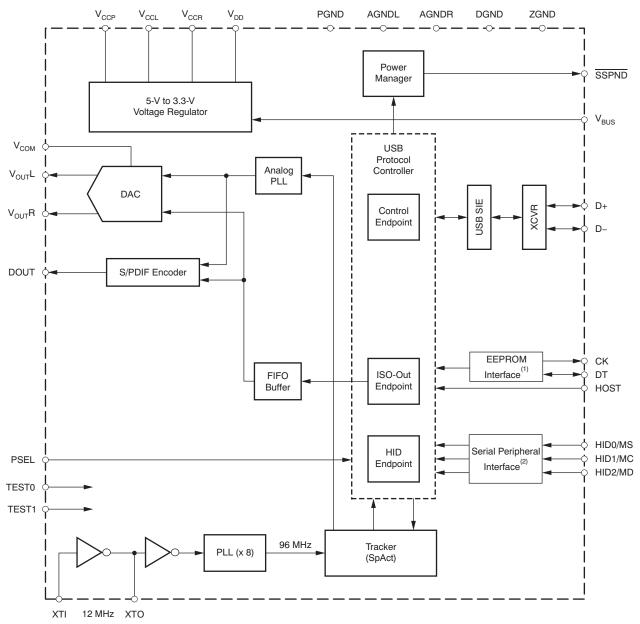

## **FUNCTIONAL BLOCK DIAGRAMS**

## PCM2704C/PCM2705C

- (1) Applies to PCM2704CDB.

- (2) Applies to PCM2705CDB.

Figure 1.

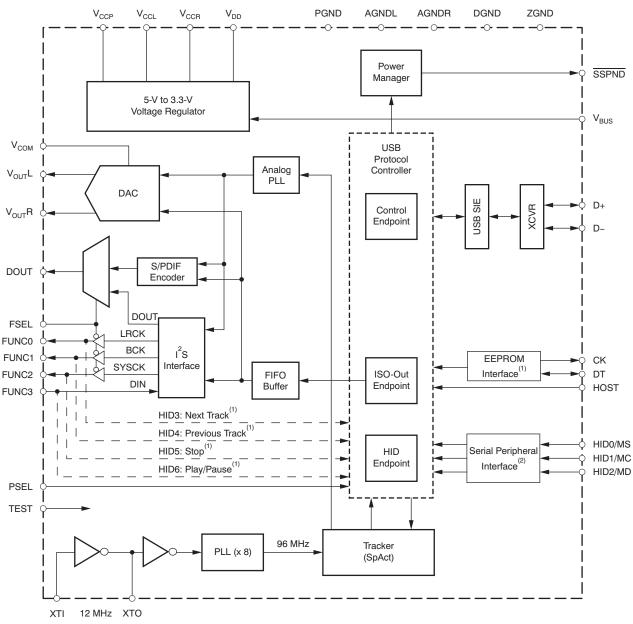

#### PCM2706C/PCM2707C

- (1) Applies to PCM2706CPJT.

- (2) Applies to PCM2707CPJT.

Figure 2.

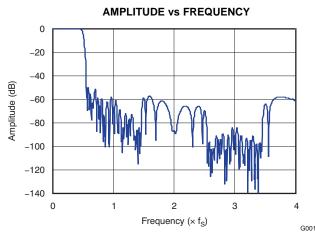

#### TYPICAL CHARACTERISTICS: INTERNAL FILTER

All specifications at  $T_A = 25$ °C,  $V_{BUS} = 5$  V,  $f_S = 44.1$  kHz,  $f_{IN} = 1$  kHz, 16-bit data (unless otherwise noted).

# **DAC Digital Interpolation Filter Frequency Response**

AMPLITUDE vs FREQUENCY 0.05 0.04 0.03 0.02 Amplitude (dB) 0.01 0 -0.01 -0.02 -0.03 -0.04 -0.05 0.5 0.1 0.2 0.3 0.4 Frequency (x f<sub>S</sub>) G002

Figure 3. Frequency Response

Figure 4. Passband Ripple

## **DAC Analog Low-Pass Filter Frequency Response**

Figure 6. Stop Band Characteristics

#### TYPICAL CHARACTERISTICS: GENERAL

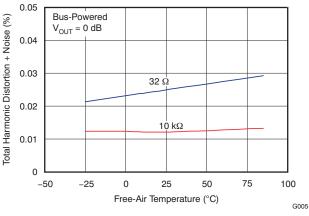

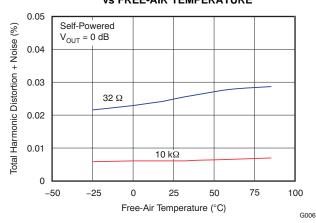

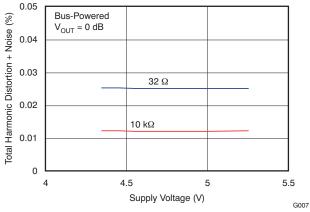

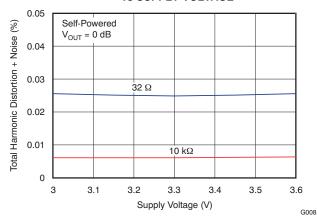

All specifications at  $T_A = +25$ °C,  $V_{BUS} = 5$  V,  $f_S = 44.1$  kHz,  $f_{IN} = 1$  kHz, and 16-bit data (unless otherwise noted).

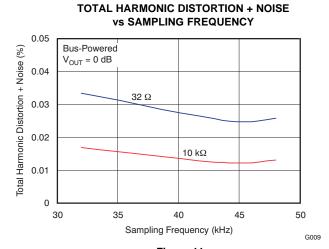

# TOTAL HARMONIC DISTORTION + NOISE vs FREE-AIR TEMPERATURE

Figure 7.

# TOTAL HARMONIC DISTORTION + NOISE vs FREE-AIR TEMPERATURE

Figure 8.

# TOTAL HARMONIC DISTORTION + NOISE vs SUPPLY VOLTAGE

Figure 9.

# TOTAL HARMONIC DISTORTION + NOISE vs SUPPLY VOLTAGE

Figure 10.

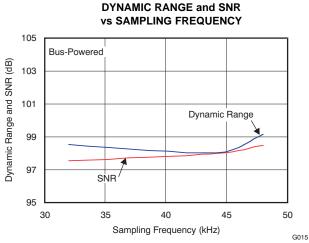

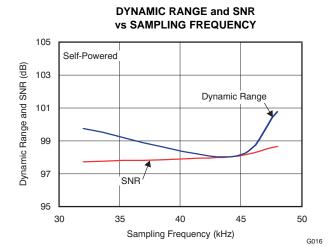

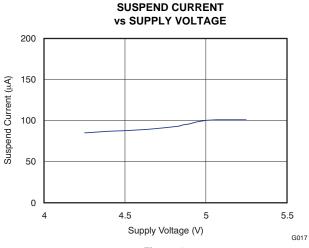

## TYPICAL CHARACTERISTICS: GENERAL (continued)

All specifications at  $T_A = +25$ °C,  $V_{BUS} = 5$  V,  $f_S = 44.1$  kHz,  $f_{IN} = 1$  kHz, and 16-bit data (unless otherwise noted).

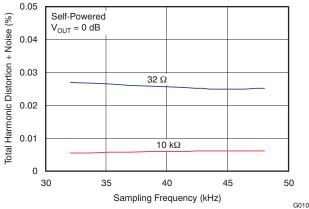

Self-Powered  $V_{OLIT} = 0 dB$

**TOTAL HARMONIC DISTORTION + NOISE**

vs SAMPLING FREQUENCY

Figure 11.

Figure 12.

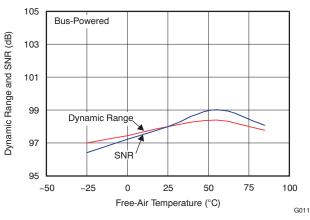

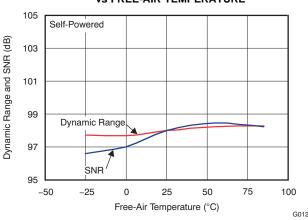

**DYNAMIC RANGE and SNR VS FREE-AIR TEMPERATURE**

Figure 13.

Figure 14.

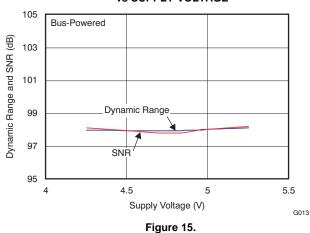

#### **DYNAMIC RANGE and SNR** vs SUPPLY VOLTAGE

**DYNAMIC RANGE and SNR vs SUPPLY VOLTAGE**

Figure 16.

## **TYPICAL CHARACTERISTICS: GENERAL (continued)**

All specifications at  $T_A = +25$ °C,  $V_{BUS} = 5$  V,  $f_S = 44.1$  kHz,  $f_{IN} = 1$  kHz, and 16-bit data (unless otherwise noted).

Figure 18.

Figure 19.

## TYPICAL CHARACTERISTICS: GENERAL (continued)

All specifications at  $T_A = +25$ °C,  $V_{BUS} = 5$  V,  $f_S = 44.1$  kHz,  $f_{IN} = 1$  kHz, and 16-bit data (unless otherwise noted).

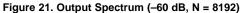

Figure 22. Output Spectrum (-60 dB, N = 8192)

#### DETAILED DESCRIPTION

#### **Clock and Reset**

For both USB and audio functions, the PCM2704C/5C/6C/7C require a 12-MHz (±500 ppm) clock that can be generated by the onboard oscillator using a 12-MHz crystal resonator. The 12-MHz crystal resonator must be connected to the XTI pin (pin 28 for the PCM2704C/5C, pin 12 for the PCM2706C/7C) and the XTO pin (pin 1 for the PCM2704C/5C, pin 13 for the PCM2706C/7C) with one large (1-MΩ) resistor and two small capacitors; the capacitance of these components depends on the specified load capacitance of the crystal resonator. An external clock can be supplied from XTI (pin 28 for the PCM2704C/5C, pin 12 for the PCM2706C/7C). If an external clock is supplied, XTO (pin 1 for the PCM2704C/5C, pin 13 for the PCM2706C/7C) must be left open. No clock disabling pin is provided; therefore, it is not recommended to use the external clock supply. SSPND (pin 27 for the PCM2704C/5C, pin 11 for the PCM2706C/7C) cannot use clock disabling.

The PCM2704C/5C/6C/7C have an internal power-on reset circuit, and it works automatically when  $V_{DD}$  (pin 7 for the PCM2704C/5C, pin 21 for the PCM2706C/7C) exceeds 2-V typical (1.6 V to 2.4 V), which is equivalent to  $V_{BUS}$  (pin 10 for the PCM2704C/5C, pin 24 for the PCM2706C/7C) exceeding 3-V typical for bus-powered applications. Approximately 700  $\mu$ s is required until an internal reset release occurs.

#### **Operation Mode Selection**

The PCM2704C/5C/6C/7C have the following mode-select pins.

## **Power Configuration Select/Host Detection**

PSEL (pin 4 for the PCM2704C/5C, pin 16 for the PCM2706C/7C) is dedicated to selecting the power source. This selection affects the configuration descriptor. While in bus-powered operation, the maximum power consumption from  $V_{BUS}$  is determined by the HOST pin (pin 21 for the PCM2704C/5C, pin 3 for the PCM2706C/7C). For self-powered operation, the HOST pin must be connected to  $V_{BUS}$  of the USB bus with a pulldown resistor to detect attach and detach. (To avoid excessive suspend current, the pulldown should be a high-value resistor.) Table 3 summarizes the power configuration select options.

PSEL

DESCRIPTION

0

Self-powered

1

Bus-powered

HOST

DESCRIPTION

0

Detached from USB (self-powered)/100 mA (bus-powered)

1

Attached to USB (self-powered)/500 mA (bus-powered)

**Table 3. Power Configuration Select**

## Function Select (PCM2706C/7C Only)

FSEL (pin 9) determines the function of the FUNC0–FUNC3 pins (pins 4, 5, 18, and 19) and DOUT (pin 17). When the  $I^2S$  interface is required, FSEL must be low. Otherwise, FSEL must be high. Table 4 lists the functionality of the FUNC0-FUNC3 pins, based on the FSEL pin.

**Table 4. Function Select**

| FSEL | DOUT                        | FUNC0                   | FUNC1                    | FUNC2                    | FUNC3                      |

|------|-----------------------------|-------------------------|--------------------------|--------------------------|----------------------------|

| 0    | Data out (I <sup>2</sup> S) | LRCK (I <sup>2</sup> S) | BCK (I <sup>2</sup> S)   | SYSCK (I <sup>2</sup> S) | Data in (I <sup>2</sup> S) |

| 1    | S/PDIF data                 | Next track (HID) (1)    | Previous track (HID) (1) | Stop (HID) (1)           | Play/pause (HID) (1)       |

(1) Valid on the PCM2706C only; no function assigned on the PCM2707C.

#### **USB** Interface

Control data and audio data are transferred to the PCM2704C/5C/6C/7C via the D+ pin (pin 9 for the PCM2704C/5C, pin 23 for the PCM2706C/7C) and D- pin (pin 8 for the PCM2704C/5C, pin 22 for the PCM2706C/7C). D+ should be pulled up with a 1.5-k $\Omega$  (±5%) resistor. To avoid back voltage in self-powered operation, the device must not provide power to the pull-up resistor on D+ while  $V_{BUS}$  of the USB port is inactive.

All data to/from the PCM2704C/5C/6C/7C are transferred at full speed. The information shown in Table 5 is provided in the device descriptor. Some parts of the device descriptor can be modified through external ROM (PCM2704C/6C) or SPI<sup>TM</sup> (PCM2705C/7C).

**Table 5. Device Descriptor**

| DEVICE DESCRIPTOR              | DESCRIPTION                                                                                               |

|--------------------------------|-----------------------------------------------------------------------------------------------------------|

| USB revision                   | 1.1 compliant                                                                                             |

| Device class                   | 0x00 (device defined interface level)                                                                     |

| Device subclass                | 0x00 (not specified)                                                                                      |

| Device protocol                | 0x00 (not specified)                                                                                      |

| Max packet size for endpoint 0 | 8 bytes                                                                                                   |

| Vendor ID                      | 0x08BB (default value, can be modified)                                                                   |

| Product ID                     | 0x27C4/0x27C5/0x27C6/0x27C7 (These values correspond to the model number, and the value can be modified.) |

| Device release number          | 1.0 (0x0100)                                                                                              |

| Number of configurations       | 1                                                                                                         |

| Vendor strings                 | BurrBrown from Texas Instruments (default value, can be modified)                                         |

| Product strings                | USB AUDIO DAC (default value, can be modified)                                                            |

| Serial number                  | Not supported                                                                                             |

The information given in Table 6 is contained in the configuration descriptor. Some parts of the configuration descriptor can be modified through external ROM (PCM2704C/6C) or SPI (PCM2705C/7C).

**Table 6. Configuration Descriptor**

| CONFIGURATION DESCRIPTOR | DESCRIPTION                                                                                                                             |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Interface                | Three interfaces                                                                                                                        |

| Power attribute          | 0x80 or 0xC0 (bus-powered or self-powered, depending on PSEL; no remote wake up. This value can be modified.)                           |

| Max power                | 0x0A, 0x32, or 0xFA (20 mA for self-powered, 100 mA or 500 mA for bus-powered, depending on PSEL and HOST. This value can be modified.) |

The information listed in Table 7 is contained in the string descriptor. Some parts of the string descriptor can be modified through external ROM (PCM2704C/6C) or SPI (PCM2705C/7C).

**Table 7. String Descriptor**

| STRING DESCRIPTOR | DESCRIPTION                                                       |

|-------------------|-------------------------------------------------------------------|

| #0                | 0x0409                                                            |

| #1                | BurrBrown from Texas Instruments (default value, can be modified) |

| #2                | USB AUDIO DAC (default value, can be modified)                    |

#### **Device Configuration**

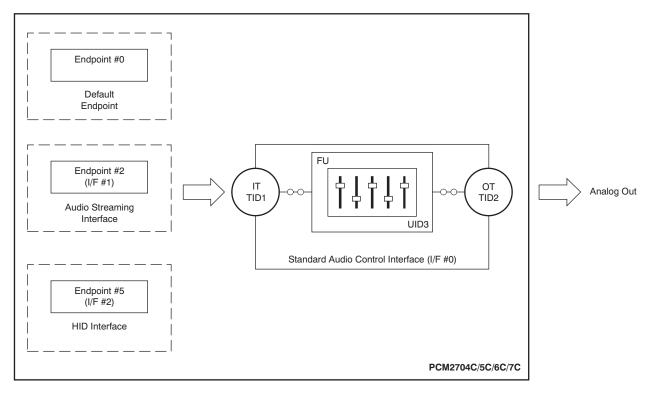

Figure 23 illustrates the USB audio function topology. The PCM2704C/5C/6C/7C have three interfaces. Each interface is enabled by different alternative settings.

Figure 23. USB Audio Function Topology

#### Interface #0 (Default/Control Interface)

Interface #0 is the control interface. Setting #0 is the only possible setting for interface #0. Setting #0 describes the standard audio control interface. The audio control interface consists of a terminal. The PCM2704C/5C/6C/7C have three terminals:

- Input terminal (IT #1) for isochronous-out stream

- Output terminal (OT #2) for audio analog output

- Feature unit (FU #3) for DAC digital attenuator

Input terminal #1 is defined as a USB stream (terminal type 0x0101). Input terminal #1 can accept two-channel audio streams consisting of left and right channels. Output terminal #2 is defined as a speaker (terminal type 0x0301). Feature unit #3 supports these sound control features:

- Volume control

- Mute control

The built-in digital volume controller can be manipulated by an audio-class-specific request from 0 dB to -64 dB in steps of 1 dB. Changes are made by incrementing or decrementing one step (that is, 1 dB) for every  $1/f_S$  time interval, until the volume level reaches the requested value. Each channel can be set to a separate value. The master volume control is not supported. A request to the master volume is stalled and ignored. The built-in digital mute controller can be manipulated by an audio-class-specific request. A master mute control request is acceptable. A mute control request to an individual channel is stalled and ignored. The digital volume control does not affect either the S/PDIF or  $I^2S$  outputs (PCM2706C/7C only).

#### Interface #1 (Isochronous-Out Interface)

Interface #1 is for the audio-streaming data-out interface. Interface #1 has the alternative settings described in Table 8. Alternative setting #0 is the zero-bandwidth setting. All other alternative settings are operational settings.

Table 8. Interface #1 Parameters

| ALTERNATIVE<br>SETTING |        | DATA FORM      | TRANSFER<br>MODE      | SAMPLING RATE<br>(kHz) |              |  |  |  |  |  |  |

|------------------------|--------|----------------|-----------------------|------------------------|--------------|--|--|--|--|--|--|

| 00                     |        | Zero bandwidth |                       |                        |              |  |  |  |  |  |  |

| 01                     | 16-bit | Stereo         | Twos complement (PCM) | Adaptive               | 32, 44.1, 48 |  |  |  |  |  |  |

| 02                     | 16-bit | Mono           | Twos complement (PCM) | Adaptive               | 32, 44.1, 48 |  |  |  |  |  |  |

#### Interface #2 (HID Interface)

Interface #2 is the interrupt-data-in interface. The HID consumer control device consists of interface #2. Alternative setting #0 is the only possible setting for interface #2.

On the HID device descriptor, eight HID items are reported for any model, in any configuration.

## **HID Items Reported**

## **Basic HID Operation**

Interface #2 can report these three key statuses for any model. These statuses can be set by the HID0–HID2 pins (PCM2704C/6C) or the SPI port (PCM2705C/7C).

- Mute (0xE2)

- Volume up (0xE9)

- Volume down (0xEA)

## Extended HID Operation (PCM2705/6/7)

By using the FUNC0–FUNC3 pins (PCM2706C) or the SPI port (PCM2705C/7C), these additional conditions can be reported to the host.

- Play/Pause (0xCD)

- Stop (0xB7)

- Previous (0xB6)

- Next (0xB5)

#### Auxiliary HID Status Report (PCM2705C/7C)

One additional HID status can be reported to the host though the SPI port. This status flag is defined by SPI command or external ROM. This definition must be described as on the report descriptor with a three-byte usage ID. *AL A/V Capture* (0x0193) is assigned as the default value for this status flag.

#### **Endpoints**

The PCM2704C/5C/6C/7C has three endpoints:

- Control endpoint (EP #0)

- Isochronous-out audio data-stream endpoint (EP #2)

- HID endpoint (EP #5)

The control endpoint is a default endpoint. The control endpoint controls all functions of the PCM2704C/5C/6C/7C by standard USB request and USB audio-class-specific request from the host. The isochronous-out audio data-stream endpoint is an audio sink endpoint that receives the PCM audio data. The isochronous-out audio data-stream endpoint accepts the adaptive transfer mode. The HID endpoint is an interrupt-in endpoint. The HID endpoint reports HID status every 10 ms.

The HID endpoint is defined as a consumer-control device. The HID function is designed as an independent endpoint from the isochronous-out endpoint. This configuration means that the effect of HID operation depends on the host software. Typically, the HID function controls the primary audio-out device.

#### DAC

The PCM2704C/5C/6C/7C have a DAC that uses an oversampling technique with 128-f<sub>S</sub>, second-order, multi-bit noise shaping. This technique provides extremely low quantization noise in the audio band, and the built-in analog low-pass filter removes the high-frequency components of the noise-shaping signal. The DAC analog outputs,  $V_{OUT}L$  and  $V_{OUT}R$ , are sent through the headphone amplifier and can provide 12 mW at 32  $\Omega$  as well as 1.8  $V_{PP}$  into a 10-k $\Omega$  load.

## Digital Audio Interface: S/PDIF Output

The PCM2704C/5C/6C/7C employ S/PDIF output. Isochronous-out data from the host are encoded to S/PDIF output DOUT, as well as to DAC analog outputs  $V_{OUT}L$  and  $V_{OUT}R$ . The interface format and timing follow the IEC-60958 standard. Monaural data are converted to the stereo format at the same data rate. S/PDIF output is not supported in the I<sup>2</sup>S I/F enable mode. The implementation of this feature is optional. Note that it is the responsibility of the user to determine whether or not to implement this feature in the end application.

#### **Channel Status Information**

Channel status information is fixed, and includes consumer application, PCM mode, copyright, and digital/digital converter data. All other bits are fixed as 0s, except for the sample frequency, which is set automatically according to the data received through the USB.

## **Copyright Management**

Digital audio data output always is encoded as original with SCMS control. Only one generation of digital duplication is allowed.

## Digital Audio Interface: I<sup>2</sup>S Interface Output (PCM2706C/7C)

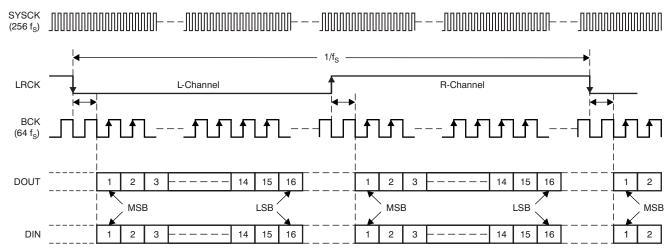

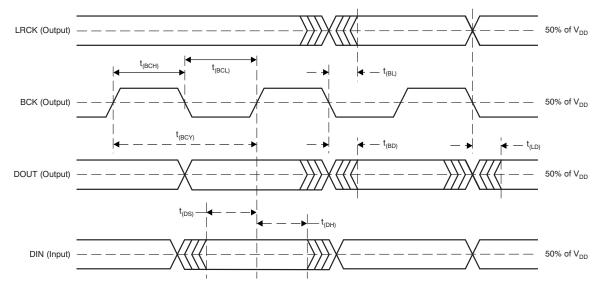

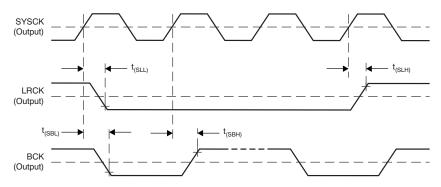

The PCM2706C and PCM2707C can support the I<sup>2</sup>S interface, which is enabled by the FSEL pin (pin 9). In the I<sup>2</sup>S interface-enabled mode, pins 4, 18, 19, 5, and 17 are assigned as DIN, SYSCK, BCK, LRCK, and DOUT, respectively. These pins provide digital output/input data in the 16-bit I<sup>2</sup>S format, which also is accepted by the internal DAC. I<sup>2</sup>S interface format and timing are shown in Figure 24, Figure 25, and Figure 26. Table 9 and Table 10 list the audio interface timing and audio clock timing characteristics, respectively.

Figure 24. Audio Data Interface Format

Figure 25. Audio Interface Timing

Table 9. Audio Interface Timing Characteristics<sup>(1)</sup>

| SYMBOL             | PARAMETER                             | MIN | MAX | UNIT |

|--------------------|---------------------------------------|-----|-----|------|

| t <sub>(BCY)</sub> | BCK pulse cycle time                  | 300 |     | ns   |

| t <sub>(BCH)</sub> | BCK pulse duration, high              | 100 |     | ns   |

| t <sub>(BCL)</sub> | BCK pulse duration, low               | 100 |     | ns   |

| t <sub>(BL)</sub>  | LRCK delay time from BCK falling edge | -20 | 40  | ns   |

| t <sub>(BD)</sub>  | DOUT delay time from BCK falling edge | -20 | 40  | ns   |

| t <sub>(LD)</sub>  | DOUT delay time from LRCK edge        | -20 | 40  | ns   |

| t <sub>(DS)</sub>  | DIN setup time                        | 20  |     | ns   |

| t <sub>(DH)</sub>  | DIN hold time                         | 20  |     | ns   |

## (1) Load capacitance of LRCK, BCK, and DOUT is 20 pF.

Figure 26. Audio Clock Timing

# Table 10. Audio Clock Timing Characteristics (1)

| SYMBOL                 | PARAMETER                              | MIN | MAX | UNIT |

|------------------------|----------------------------------------|-----|-----|------|

| $t_{(SLL)}, t_{(SLH)}$ | LRCK delay time from SYSCK rising edge | -5  | 10  | ns   |

| $t_{(SBL)}, t_{(SBH)}$ | BCK delay time from SYSCK rising edge  | -5  | 10  | ns   |

(1) Load capacitance is 20 pF.

#### **DESCRIPTOR DATA MODIFICATION**

The descriptor data can be modified through the  $I^2C^{TM}$  port by external ROM (PCM2704C/6C) or through the SPI port by an SPI host such as an MCU (PCM2705C/7C) under a particular configuration of the PSEL and HOST pins. Setting both the PSEL and the HOST pins high is necessary to modify the descriptor data; the D+ pin pull-up resistor must not be activated before programming the descriptor data through the external ROM or SPI port is completed. The descriptor data must be sent from an external ROM to the PCM2704C/6C or from the SPI host to the PCM2705C/7C in LSB first format, with a specified byte order. Additionally, the power attribute and max power contents must be consistent with the PSEL setting and the power usage from the USB  $V_{BUS}$  of the end application. Therefore, descriptor data modification in self-powered configuration (PSEL = low) is not supported.

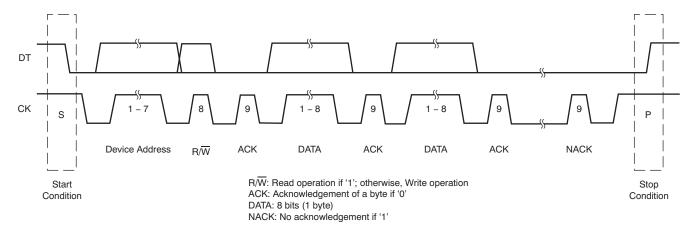

## External ROM Descriptor (PCM2704C/6C)

The PCM2704C/6C support an external ROM interface to override internal descriptors. Pin 3 (for the PCM2704C) or pin 15 (for the PCM2706C) is assigned as DT (serial data), and pin 2 (for the PCM2704C) or pin 14 (for the PCM2706C) is assigned as CK (serial clock) of the I<sup>2</sup>C interface when using the external ROM descriptor. Descriptor data are transferred from the external ROM to the PCM2704C/6C through the I<sup>2</sup>C interface the first time when the device is activate after a power-on reset. Before completing a read of the external ROM, the PCM2704C/6C reply with *NACK* for any USB command request from the host to the device itself. The descriptor data, which can be in the external ROM, must meet these parameters:

- String descriptors must be described in ANSI ASCII code (1 byte for each character).

- String descriptors are converted automatically to unicode strings for transmission to the host.

- The device address of the external ROM is fixed as 0xA0.

The data bits must be sent from LSB to MSB on the  $I^2C$  bus. This condition means that each byte of data must be stored with its bits in reverse order. A read operation is performed at a frequency of XTI/384 (approximately 30 kHz). The power attribute and max power contents must be consistent with the end application circuit configuration (the PSEL setting and the actual power usage from  $V_{BUS}$  of the USB connector); otherwise, it may cause improper or unexpected PCM2704C/6C operation.

The data must be stored from address 0x00 and must consist of 57 bytes, according to the parameters listed below:

- Vendor ID (2 bytes)

- Product ID (2 bytes)

- Product string (16 bytes in ANSI ASCII code)

- Vendor string (32 bytes in ANSI ASCII code)

- Power attribute (1 byte)

- Max power (1 byte)

- Auxiliary HID usage ID in report descriptor (3 bytes)

Figure 27 illustrates the timing for an external ROM read operation. The timing characteristics are summarized in Table 11.

Figure 27. External ROM Read Operation

**Table 11. External ROM Read Operation Characteristics**

|   |                |     |     |      | _   |      |     |   |      |   |

|---|----------------|-----|-----|------|-----|------|-----|---|------|---|

| M | М              | М   | S   | S    | М   | S    | М   | S | М    | M |

| S | Device address | R/W | ACK | DATA | ACK | DATA | ACK |   | NACK | Р |

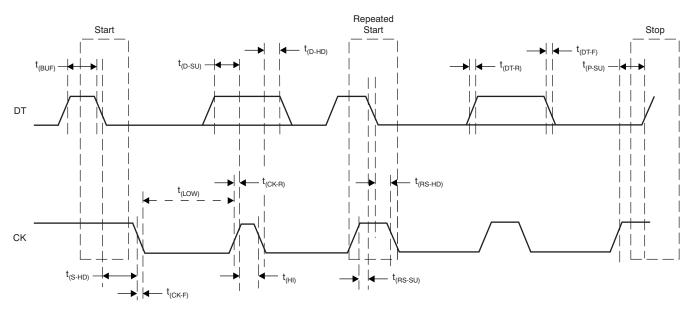

Figure 28 shows the timing for an external ROM read interface. The respective timing characteristics are summarized in Table 12.

Figure 28. External ROM Read Interface Timing Requirements

**Table 12. External ROM Read Interface Timing Characteristics**

| SYMBOL                     | PARAMETER                                                                   | MIN                     | MAX  | UNIT |

|----------------------------|-----------------------------------------------------------------------------|-------------------------|------|------|

| f <sub>(CK)</sub>          | CK clock frequency                                                          |                         | 100  | kHz  |

| t <sub>(BUF)</sub>         | Bus free time between a STOP and a START condition                          | 4.7                     |      | μs   |

| $t_{(LOW)}$                | Low period of the CK clock                                                  | 4.7                     |      | μs   |

| t <sub>(HI)</sub>          | High period of the CK clock                                                 | 4                       |      | μs   |

| t <sub>(RS-SU)</sub>       | Setup time for START/repeated START condition                               | 4.7                     |      | μs   |

| $t_{(S-HD)} \ t_{(RS-HD)}$ | Hold time for START/repeated START condition                                | 4                       |      | μs   |

| t <sub>(D-SU)</sub>        | Data setup time                                                             | 250                     |      | ns   |

| t <sub>(D-HD)</sub>        | Data hold time                                                              | 0                       | 900  | ns   |

| t <sub>(CK-R)</sub>        | Rise time of CK signal                                                      | 20 + 0.1 C <sub>B</sub> | 1000 | ns   |

| t <sub>(CK-F)</sub>        | Fall time of CK signal                                                      | 20 + 0.1 C <sub>B</sub> | 1000 | ns   |

| t <sub>(DT-R)</sub>        | Rise time of DT signal                                                      | 20 + 0.1 C <sub>B</sub> | 1000 | ns   |

| t <sub>(DT-F)</sub>        | Fall time of DT signal                                                      | 20 + 0.1 C <sub>B</sub> | 1000 | ns   |

| t <sub>(P-SU)</sub>        | Setup time for STOP condition                                               | 4                       |      | μs   |

| C <sub>B</sub>             | Capacitive load for DT and CK lines                                         |                         | 400  | pF   |

| $V_{NH}$                   | Noise margin at high level for each connected device (including hysteresis) | 0.2 V <sub>DD</sub>     |      | V    |

Texas

# www.ti.com

## **External ROM Example**

#### External ROM data (sample set)

```

0xBB, 0x08, 0x04, 0x27, 0x50, 0x72, 0x65, 0x64, 0x75, 0x63, 0x74, 0x20, 0x73, 0x74, 0x72, 0x69, 0x6E, 0x67, 0x73, 0x2E, 0x56, 0x65, 0x6E, 0x64, 0x6F, 0x72, 0x20, 0x73, 0x74, 0x72, 0x69, 0x6E, 0x67, 0x73, 0x20, 0x61, 0x72, 0x65, 0x20, 0x70, 0x6C, 0x61, 0x63, 0x65, 0x64, 0x20, 0x68, 0x65, 0x72, 0x65, 0x2E, 0x20, 0x70, 0x70,

```

#### **Explanation**

Data are stored beginning at address 0x00.

Vendor ID: 0x08BB Product ID: 0x2704

**Product string:** Product strings (16 bytes).

Vendor string: Vendor strings are placed here (32 bytes, 31 visible characters are followed by 1 space).

Power attribute (bmAttribute): 0x80 (Bus-powered).

Max power (maxPower): 0x7D (250 mA).

Auxiliary HID usage ID: 0x0A, 0x93, 0x01 (AL A/V capture).

Note that the data bits must be sent from LSB to MSB on the I<sup>2</sup>C bus. Therefore, each data byte must be stored with its bits in reverse order.

SBFS036A - AUGUST 2011-REVISED JULY 2012

INSTRUMENTS

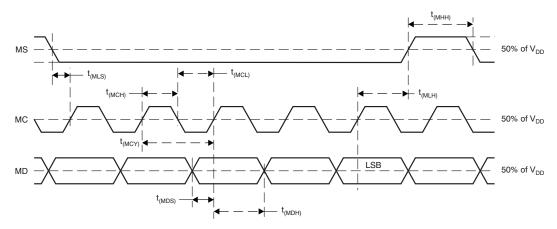

# Serial Programming Interface (PCM2705C/7C)

The PCM2705C/7C supports a serial interface (SPI) to program the descriptor and to set the HID state. Descriptor data are described in the External ROM Descriptor section. Figure 29 illustrates the SPI timing; Table 13 lists the respective timing characteristics.

Figure 29. SPI Timing Diagram

**Table 13. SPI Timing Characteristics**

| SYMBOL             | PARAMETER                         | MIN | MAX | UNIT |

|--------------------|-----------------------------------|-----|-----|------|

| t <sub>(MCY)</sub> | MC pulse cycle time               | 100 |     | ns   |

| t <sub>(MCL)</sub> | MC low-level time                 | 50  | ns  |      |

| t <sub>(MCH)</sub> | MC high-level time                | 50  |     | ns   |

| t <sub>(MHH)</sub> | MS high-level time                | 100 | ns  |      |

| t <sub>(MLS)</sub> | MS falling edge to MC rising edge | 20  |     | ns   |

| t <sub>(MLH)</sub> | MS hold time                      | 20  |     | ns   |

| t <sub>(MDH)</sub> | MD hold time                      | 15  |     | ns   |

| t <sub>(MDS)</sub> | MD setup time                     | 20  |     | ns   |

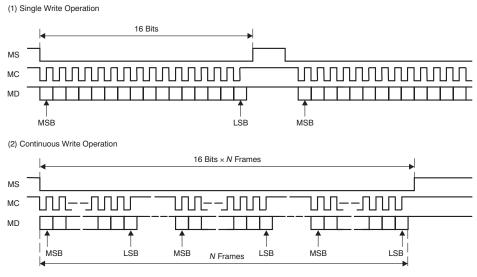

Figure 30 shows the SPI write timing sequence.

Figure 30. SPI Write Operation

## SPI Register (PCM2705C/7C)

## **Table 14. SPI Register Description**

| B15 | B14 | B13 | B12 | B11 | B10 | В9   | B8 | B7 | В6 | B5 | B4 | В3 | B2 | B1 | В0 |

|-----|-----|-----|-----|-----|-----|------|----|----|----|----|----|----|----|----|----|

| 0   | 0   | 0   | 0   | ST  | 0   | ADDR | 0  | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 |

#### D[7:0] Function of the lower 8 bits depends on the value of the ST (B11) bit.

ST = 0 (HID status write)

- D7 Reports MUTE HID status to the host (active high)

- D6 Reports volume-up HID status to the host (active high)

- D5 Reports volume-down HID status to the host (active high)

- D4 Reports next-track HID status to the host (active high)

- D3 Reports previous-track HID status to the host (active high)

- D2 Reports stop HID status to the host (active high)

- D1 Reports play/pause HID status to the host (active high)

- D0 Reports extended command status to the host (active high)

ST = 1 (ROM data write)

D[7:0] Internal descriptor ROM data, D0:LSB, D7:MSB

Contents of the power attribute and max power must be consistent with the actual application circuit configuration (the PSEL setting and the actual power usage from  $V_{BUS}$  of the USB connector); otherwise, it may cause improper or unexpected PCM2705C/7C operation.

#### ADDR Starts write operation for internal descriptor reprogramming (active high)

This bit resets the descriptor ROM address counter and indicates that subsequent words should be ROM data (described in the *External ROM Example* section). 456 bits of ROM data must be continuously followed after this bit has been asserted. The data bits must be sent from LSB (D0) to MSB (D7).

To set ADDR high, ST must be set low. Note that the lower 8 bits are still active as an HID status write when ST is set low.

ST Determines the function of the lower 8-bit data. Table 15 summarizes the functionality of ST and ADDR bit combinations.

0: HID status write

1: Descriptor ROM data write

Table 15. Functionality of ST and ADDR Bit Combinations

| ST | ADDR | FUNCTION                                          |  |  |  |  |  |

|----|------|---------------------------------------------------|--|--|--|--|--|

| 0  | 0    | HIS status write                                  |  |  |  |  |  |

| 0  | 1    | HIS status write and descriptor ROM address reset |  |  |  |  |  |

| 1  | 0    | Descriptor ROM data write                         |  |  |  |  |  |

| 1  | 1    | Reserved                                          |  |  |  |  |  |

#### **USB Host Interface Sequence**

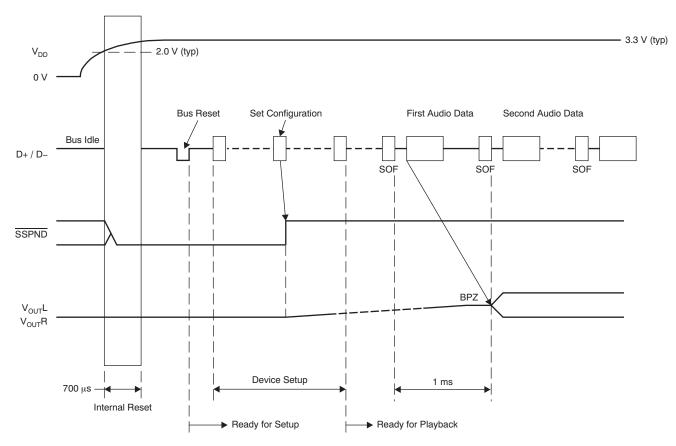

## Power-On, Attach, and Playback Sequence

The PCM2704C/5C/6C/7C are ready for setup when the reset sequence has finished and the USB bus is attached. After a connection has been established (through the set-up process), the PCM2704C/5C/6C/7C are ready to accept USB audio data. While waiting for the audio data (that is, the device is in an idle state), the analog output is set to bipolar zero (BPZ).

Upon receiving the audio data, the PCM2704C/5C/6C/7C stores the first audio packet into the internal storage buffer. The packet contains 1 ms of audio data. The PCM2704C/5C/6C/7C start playing the audio data after detecting the next subsequent start-of-frame (SOF) packet. Figure 31 shows the initial operation sequence for the device.

Figure 31. Initial Sequence

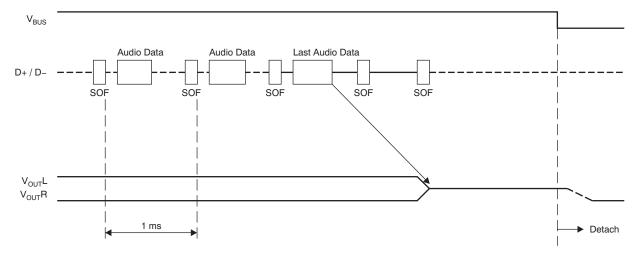

#### Play, Stop, and Detach Sequence

When the host finishes or aborts playback, the PCM2704C/5C/6C/7C stop playing after the last audio data output is complete. Figure 32 illustrates the play, stop, and detach sequence.

Figure 32. Play, Stop, and Detach Sequence

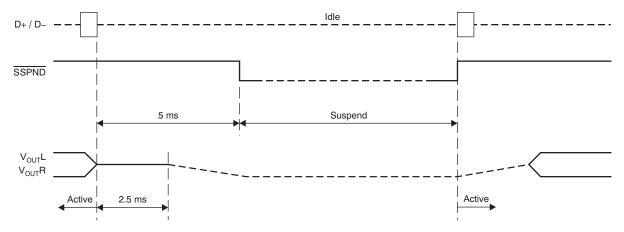

## **Suspend and Resume Sequence**

The PCM2704C/5C/6C/7C enter a suspended state after the USB bus has been in a constant idle state for approximately 5 ms. While the PCM2704C/5C/6C/7C are in this suspended state, the SSPND flag (pin 27 for the PCM2704C/5C, pin 11 for the PCM2706C/7C) is asserted. The PCM2704C/5C/6C/7C wake up immediately when detecting a non-idle state on the USB bus. Figure 33 shows the operating sequence for the suspend and resume process.

Figure 33. Suspend and Resume

#### **EXAMPLE CIRCUITS**

## **Operating Environment**

For current information on the PCM2704C/2705C/2706C/2707C operating environments, see the *Updated Operating Environments for PCM270X, PCM290X Applications* application report, SLAA374, available through the TI website at www.ti.com.

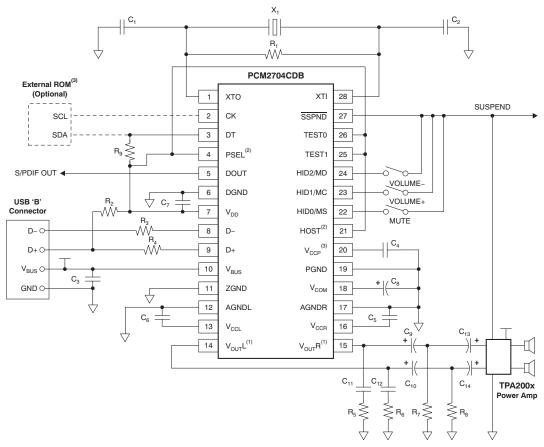

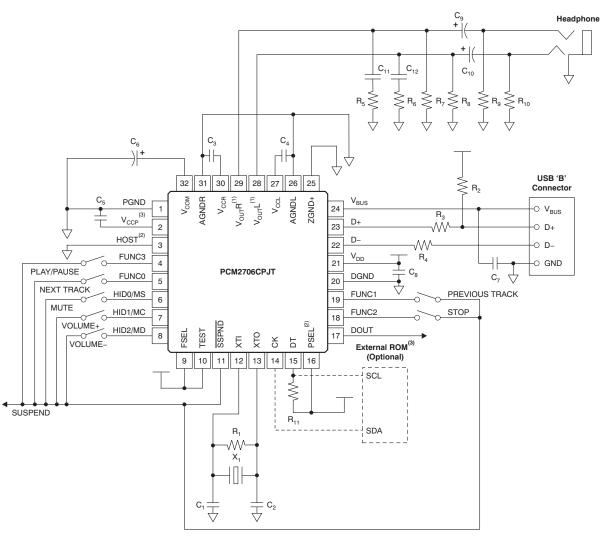

## **Typical Circuit Connection 1: USB Speaker**

Figure 34 illustrates a typical circuit connection for an internal-descriptor, bus-powered, 500-mA application.

NOTE:  $X_1$ : 12-MHz crystal resonator.  $C_1$ ,  $C_2$ : 10-pF to 33-pF capacitors (depending on load capacitance of crystal resonator).  $C_3$ to  $C_7$ : 1- $\mu$ F ceramic capacitors.  $C_8$ : 10- $\mu$ F electrolytic capacitor.  $C_9$ ,  $C_{10}$ : 100- $\mu$ F electrolytic capacitors (depending on tradeoff between required frequency response and discharge time for resume).  $C_{11}$ ,  $C_{12}$ : 0.022- $\mu$ F ceramic capacitors.  $C_{13}$ ,  $C_{14}$ : 1- $\mu$ F electrolytic capacitors.  $C_{11}$ ,  $C_{12}$ : 0.022- $\mu$ F ceramic capacitors.  $C_{13}$ ,  $C_{14}$ : 1- $\mu$ F electrolytic capacitors.  $C_{11}$   $C_{12}$ : 0.022- $C_{11}$   $C_{12}$ : 0.022- $C_{13}$   $C_{13}$   $C_{14}$ : 1- $C_{12}$   $C_{13}$   $C_{14}$ : 1- $C_{15}$   $C_{15$

- (1) Output impedance of  $V_{OUT}L$  and  $V_{OUT}R$  during suspended mode or lack of power supply is 26 k $\Omega$  ±20%, which is the discharge path for  $C_9$  and  $C_{10}$ .

- (2) Descriptor programming through external ROM is only available when PSEL and HOST are high.

- (3) External ROM power can be supplied from  $V_{CCP}$ , but any other active component must not use  $V_{CCP}$ ,  $V_{CCL}$ ,  $V_{CCR}$ , or  $V_{DD}$  as a power source.

Figure 34. Bus-Powered Application

#### **NOTE**

The circuit illustrated in Figure 34 is for information only. The entire board design should be considered to meet the USB specification as a USB-compliant product.

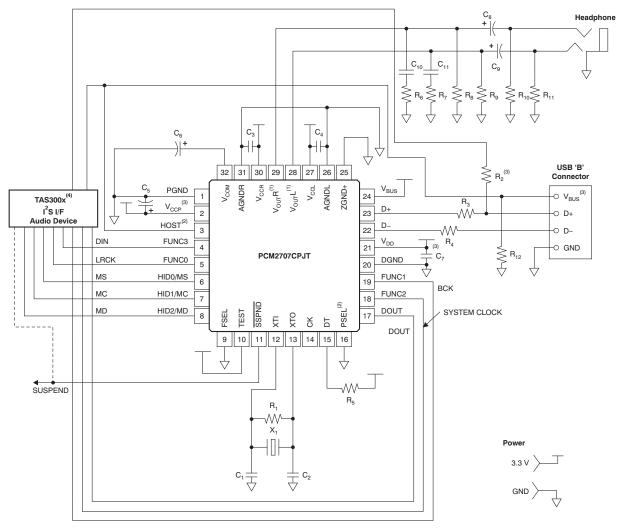

## **Typical Circuit Connection 2: Remote Headphone**

Figure 35 illustrates a typical circuit connection for a bus-powered, 100-mA headphone with seven HIDs.

NOTE:  $X_1$ : 12-MHz crystal resonator.  $C_1$ ,  $C_2$ : 10-pF to 33-pF capacitors (depending on load capacitance of crystal resonator).  $C_3$  to  $C_5$ ,  $C_7$ ,  $C_8$ : 1-µF ceramic capacitors.  $C_6$ : 10-µF electrolytic capacitor.  $C_9$ ,  $C_{10}$ : 100-µF electrolytic capacitors (depending on required frequency response).  $C_{11}$ ,  $C_{12}$ : 0.022-µF ceramic capacitors.  $C_{11}$ : 1-M $\Omega$  resistor.  $C_{12}$ : 1.5-k $\Omega$  resistors.  $C_{13}$ : 22- $\Omega$  resistors.  $C_{14}$ : 1.6- $C_{15}$ : 1.

- (1) Output impedance of  $V_{OUT}L$  and  $V_{OUT}R$  during suspend mode or lack of power supply is 26 k $\Omega$  ±20%, which is the discharge path for  $C_9$  and  $C_{10}$ .