# **UM7108 Series**

# One Chip 3 1/2-Digit Digital Multimeter

#### **Features**

- Multi-function measurement system:

- · Analog to digital converter

- Data hold and Peak hold, both with LCD annunciators

- Short circuit beeper with LCD annunciator

- · Low battery detector with LCD annunciator

- Frequency counter with two LCD annunciators (UM7108F)

- Frequency counter: Auto range from 2 KHz to 20 MHz

- Triplex LCD display

- Full 3 1/2-Digit Display

- 6 annunciators Data-hold, Peak-hold, KHz, MHz, Low-bat, Continuance

- · 1 annunciator drive pin for unit display

- 3 decimal point drivers with 3 independent control pins

- · Polarity driver

- · Displays "OL" for input overrange

- Provides serial data output for other applications (UM7108F)

- Guaranteed zero reading with zero input

- True polarity indication for precision null detection

- Convenient 9V battery operation

- Low power operation 10mW

- Low noise A/D converter

- Lownoise --- 15 μV

- · Differential inputs 1 pA bias current

- Differential reference for ratiometric ohms

- On-chip voltage reference 20 ppM/°C drift

- · Low linearity error guaranteed less than 1 count

- High Impedance CMOS differential inputs —10<sup>12</sup> Ω

- Applications: digital panel meters, digital multi meters, thermometers, capacitance meters, pH meters, photometers etc.

### **General Description**

The UM7108 is a one chip 3 1/2-Digit Digital Multimeter which combines an integrated A/D converter, peak-hold, data-hold, short circuit beeper and low battery detector in a 40-pin DIP. The UM7108F 48-pin QFP includes a frequency counter, and serial data output.

In UM7108, an autozero cycle guarantees a zero reading with a 0 Volt input. CMOS structure reduces analog input bias current to only 1 pA and low power consumption. Rollover error is less than 1 count. Differential reference inputs permit ratiometric measurements for resistor or bridge transducer applications.

A 'PEAK-HOLD' input allows the UM7108 to hold the highest A/D readout. This feature is useful in measuring the starting current of motors, maximum temperatures and similar applications. However, the 'DATA-HOLD' input allows the UM7108 to hold the current A/D readout or frequency readout. This feature is useful in measuring unstable measurements

or in preventing abnormal inputs which may confuse the measurements.

The frequency counter is auto ranging from 2 KHz to 20 MHz over a five decade range with KHz and MHz annunciators, which are useful in measuring normal frequencies.

Short circuit beeper will sound whenever the readout is less than 30 after enabling the short circuit beeper. This feature is useful in detecting short circuits without watching the LCD.

The UM7108 provides 3 independent decimal point driving pins for the manufacturer to determine which decimal point is displayed. The 3 decimal point drivers are built-in in UM7108. The UM7108 also provides one annunciator pin for manufacturer to easily display the unit on LCD. With the above features, the total system cost of a 3 1/2-digit digital multimeter will be reduced by using UM7108. The UM7108 operates from a 9 volt battery, same as UM7106, with typical power of 10 mW; and the packages include 40-pin DIP and 48-pin quad flat pack.

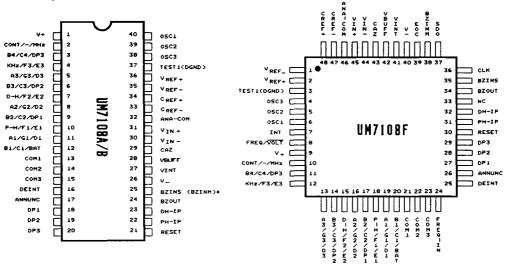

### **Pin Configurations**

\* Note: Pin 25 | BZINS- UM7108A BZINM- UM7107B

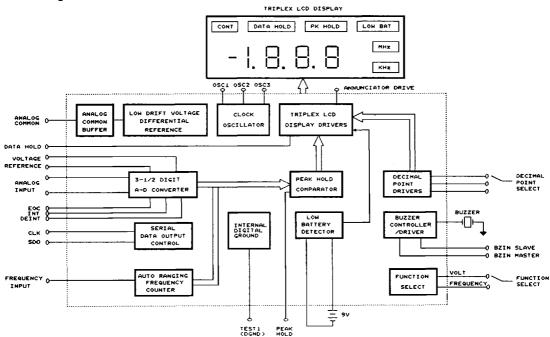

### **Block Diagram**

### **Absolute Maximum Ratings\***

| Supply Voltage (V+ to V-)                      |

|------------------------------------------------|

| Analog Input Voltage (either input)V+ to V-    |

| Reference Input Voltage (either input)V+ to V- |

| Clock Input Test to V+                         |

| Power Dissipation                              |

| Operating Temperature                          |

| Storage Temperature                            |

| Lead Temperature (Soldering, 10 sec)260°C      |

### \*Comments

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of this device at these or any other conditions above those indicated in the operational sections of this specification is not implied and exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **DC Electrical Characteristics**

Unless otherwise noted, specifications apply to UM7108 at Vsupply (V+ to V-) = 9.0V, TA = 25°C, Fclock = 40 KHz

| Parameter                                                     | Symbol   | Min.         | Тур.         | Max.   | Unit               | Conditions                                     |

|---------------------------------------------------------------|----------|--------------|--------------|--------|--------------------|------------------------------------------------|

| Zero input<br>Reading                                         | _        | -000.0       | ±000.0       | +000.0 | Digital<br>Reading | Vin = 0.0V<br>Full Scale = 200.0mV             |

| Ratiometric Reading                                           | -        | 999          | 999/<br>1000 | 1000   | Digital<br>Reading | Vin = Vref<br>Vref = 100.0mV                   |

| Linearity<br>(Max. Deviation From Best<br>Straight Line Fit)  | _        | <b>-1</b>    | ±0.2         | _+1    | Counts             | Full Scale 200.0 mV<br>or 2.000V               |

| Noise                                                         | Vn       | -            | 15           | -      | μ٧                 | Vin = 0V<br>Full Scale 200.0mV                 |

| Leakage Current Input                                         | İLEAK    | -            | 1            | 10     | pA                 | Vin = 0V                                       |

| Zero Reading Drift                                            | -        | -            | 0.2          | 1      | μV/°C              | Vin = 0V<br>0° < TA < 70°C                     |

| Scale Factor Temp Coeff                                       | -        | <del>-</del> | 1            | 5      | ppm/°C             | Vin = 199.0mV<br>0° < TA < 70°C                |

| Analog Common Voltage<br>(With Respect to Positive<br>Supply) | Vana-com | 2.8          | 3.0          | 3.2    | v                  | 25K a Between<br>Common and Positive<br>Supply |

| Temp Coeff of Analog<br>Common                                | -        | -            | 20           | 50     | ppm/°C             | 25K   Between  Common and Pos Supply           |

| Common-mode Rejection<br>Ratio                                | -        |              | 50           | 200    | μV/V               | Vcm =±1V, Vin = 0V<br>Full-scale = 200.0mV     |

# **DC Electrical Characteristics (continued)**

| Parameter                                                   | Symbol      | Min.        | Тур.     | Max.         | Unit        | Conditions            |

|-------------------------------------------------------------|-------------|-------------|----------|--------------|-------------|-----------------------|

| Supply Current<br>(Doesn't include LCD and<br>Com. Current) | †DD         | _           | 1.2      | 1.8          | mA          | Is (Vin = 0.0V)       |

| LCD Pk-Pk<br>Segment Drive Voltage                          | VLCDS       | 4           | 5        | 6            | V           |                       |

| LCD Pk-Pk<br>Back Plane Drive Voltage                       | VLCDS       | 4           | 5        | 6            | ٧           |                       |

| Rollover Error                                              | -           | -1          | ±0.2     | +1           | Counts      | Vin+ = Vin- = 200.0mV |

| Frequency counter                                           |             | V+ - 1.0    | -        | -            | ٧           | Vih(FREQ)             |

| input level                                                 | VFRE        | -           | -        | DGND+1.0     | ٧           | Vil(FREQ)             |

| Low battery margin                                          | VLOW        | 6.7         | 7.2      | 7.7          | V           | ( between V+ to V- )  |

| Input terminal: BZINM, BZ                                   | INS, PH-IP, | DH-IP, RESE | T, FREQ/ | VOLT, CLK, I | OP1, DP2, D | )P3                   |

| Input logic low voltage                                     | Vil         | _           | -        | DGND+1.5     | ٧           |                       |

| Input logic high voltage                                    | Vih         | V+ - 1.5    |          | -            | ٧           |                       |

| Pull down current                                           | lpd         | -           | 5        | -            | μΑ          | Vin = V+              |

| Output terminal: EOC, SDO,                                  | INT, DEINT  |             |          | l            |             | 1                     |

| Output logic low voltage                                    | Vol         | DGND        | _        | DGND+0.5     | V           |                       |

| Output logic high voltage                                   | Voн         | V+ - 0.5    | _        | V+           | ٧           |                       |

### **AC Characteristics**

| Parameter            | Symbol | Min.    | Тур. | Max. | Unit | Conditions |

|----------------------|--------|---------|------|------|------|------------|

| Peak-hold duration   | Tph    | 0.8     | -    | -    | sec  |            |

| PH-IP and DH-IP Keys |        | 2708¥ 2 |      |      | 1    |            |

| Keydebouncetime      | Tdeb   | _       | 32   | 38   | ms   |            |

| Key hold time        | Tan    | 50      | -    | _    | ms   |            |

# AC Characteristics (continued)

| Parameter                        | Symbol | Min. | Тур. | Max. | Unit | Conditions |

|----------------------------------|--------|------|------|------|------|------------|

| LCD display frequency            | Flod , | -    | 167  | -    | Hz   |            |

| Operating frequency              | Fclock |      | 40   | _    | KHz  |            |

| Buzzer drive frequency           | Fbzout | -    | 2.5  | _    | KHz  |            |

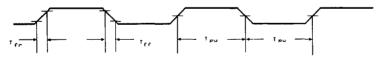

| FREQ-IN Waveform<br>Rising Time  | Tfr    | -    | -    | 20   | ns   |            |

| FREQ-IN Waveform<br>Falling Time | Tff    | _    |      | 20   | ns   |            |

| FREQ-IN Waveform<br>Pulse Width  | Трw    | 17   | -    | _    | ns   |            |

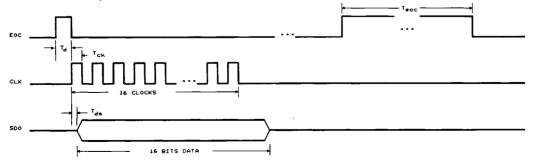

| Clock Delay Time                 | Td     | 1    |      | 5000 | με   | -          |

| Data Set-up Time                 | Tds    | -    |      | 500  | ns   |            |

| EOCPulseWidth                    | Teoc   | -    | -    | 10   | ms   |            |

| Clock Pulse Width                | Tck    | 500  | -    | -    | ns   |            |

# **Timing Waveforms**

# 1. Frequency Counter Input Waveform

### 2. Serial Data Output

# Timing Waveforms (continued)

# 3. INT, DEINT Output Waveform

# **Pin Descriptions**

| Pin N     | lo.     | <b>.</b>    |                                                                                                                                                                                                                 |

|-----------|---------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UM7108A/B | UM7108F | Designation | Description                                                                                                                                                                                                     |

| 1         | 9       | V+          | Positive supply voltage                                                                                                                                                                                         |

|           | 7       | INT         | Integrate phase indicator. This pin is logic LOW normally but goes HIGH when integrate phase begins; goes LOW when integrate phase ends                                                                         |

|           | 8       | FREQ/VOLT   | Frequency counter/voltage measurement select pin. Connecting to V+ will enable the frequency counter, connecting to TEST1 or open will execute voltage measurement. This pin is internally pulled-down to TEST1 |

| 2         | 10      | CONT/- /MHz | LCD segment drive for continuity, polarity and mega-Hz                                                                                                                                                          |

| 3         | 11      | B4/C4/DP3   | LCD segment drive for "b" and "c" segments of MSD and decimal point 3                                                                                                                                           |

| 4         | 12      | KHz/F3/E3   | LCD segment drive for kilo-Hz and " f " and "e" segments of 3rd LSD                                                                                                                                             |

| 5         | 13      | A3/G3/D3    | LCD segment drive for "a" , "g" and "d" segments of 3rd LSD                                                                                                                                                     |

| 6         | 14      | B3/C3/DP2   | LCD segment drive for "b" and "c" segments of 3rd LSD and decimal point 2                                                                                                                                       |

| 7         | 15      | D-H/F2/E2   | LCD segment drive for data-hold, " f " and "e" segments of 2nd LSD                                                                                                                                              |

| Pin N     | lo.     | <b>.</b>    |                                                                                                                                                                    |

|-----------|---------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UM7108A/B | UM7108F | Designation | Description                                                                                                                                                        |

| 8         | 16      | A2/G2/D2    | LCD segment drive for "a", "g" and "d" segments of 2nd LSD                                                                                                         |

| 9         | 17      | B2/C2/DP1   | LCD segment drive for "b" and "c" segments of 2nd LSD and decimal point 1                                                                                          |

| 10        | 18      | P-H/F1/E1   | LCD segment drive for peak-hold and " f " and "e" segments of LSD                                                                                                  |

| 11        | 19      | A1/G1/D1    | LCD segment drive for "a", "g" and "d" segments of LSD                                                                                                             |

| 12        | 20      | B1/C1/BAT   | LCD segment drive for "b" and "c" segments of LSD and low battery                                                                                                  |

| 13        | 21      | COM1        | LCD common driver #1                                                                                                                                               |

| 14        | 22      | COM2        | LCD common driver #2                                                                                                                                               |

| 15        | 23      | СОМЗ        | LCD common driver #3                                                                                                                                               |

|           | 24      | FREQ - IN   | Frequency counter input pin                                                                                                                                        |

| 16        | 25      | DEINT       | De-integrate phase indicator. This pin is logic LOW normally but goes HIGH when de-integrate phase begins; goes LOW when de-integrate phase ends                   |

| 17        | 26      | ANNUNC      | Square wave output at the LCD backplane frequency, synchronized to COM1. Connecting an LCD segment to ANNUNC pin turns it on; connecting to backplane turns it off |

| 18        | 27      | DP1         | 1st decimal point select input for voltage measurement. This pin is internally pulled-down to TEST1                                                                |

| 19        | 28      | DP2         | 2nd decimal point select input for voltage<br>measurement. This pin is internally pulled<br>down to TEST1                                                          |

| Pin t           | No.     | Desirentia  | Description                                                                                                                                                                                                                                                                                                            |

|-----------------|---------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UM7108A/B       | UM7108F | Designation | Description                                                                                                                                                                                                                                                                                                            |

| 20              | 29      | DP3         | 3rd decimal point select input for voltage measurement. This pin is internally pulled down to TEST1                                                                                                                                                                                                                    |

| 21              | 30      | RESET       | Reset input pin. Connecting to V+ will cancel both Peak-hold and Data-hold functions. This pin is internally pulled-down to TEST1                                                                                                                                                                                      |

| 22              | 31      | PH - IP     | Peak-hold input pin. Connecting to V+ will make the converter only update the readout if a new conversion value is greater than the preceding value. This pin is a toggle type input pin and is internally pulled-down to TEST1                                                                                        |

| 23              | 32      | DH - IP     | Data-hold input pin. Connecting to V+ will make the converter hold the current readout and the converter operation.  This pin is a toggle type input pin and is internally pulled-down to TEST1                                                                                                                        |

|                 | 33      | NC          | No connection                                                                                                                                                                                                                                                                                                          |

| 24              | 34      | BZOUT       | Piezo buzzer output. 2.5 KHz audio frequency output can drive a piezo buzzer  1. Whenever the readout is less than 30 and BZINS is connected to V+, BZOUT will generate a 2.5 KHz sound output.  2. Whenever the BZINM is connected to V+ it will force the BZOUT to generate a 2.5KHz sound audio output continuously |

| 25<br>(UM7108A) | 35      | BZINS       | Buzzer control slave input. This pin is internally pulled-down to TEST1. See BZOUT                                                                                                                                                                                                                                     |

|                 | 36      | CLK         | External clock input pin for serial data accessing, normally this clock signal is generated by external microcontroller                                                                                                                                                                                                |

|                 | 37      | SDO         | Serial data output pin                                                                                                                                                                                                                                                                                                 |

| 25<br>(UM7108B) | 38      | BZINM       | Buzzer control master pin. This pin is internally pulled-down to TEST1. See BZOUT                                                                                                                                                                                                                                      |

| Pin f     | No.     | Danimatian  | Paradatian                                                                                                                                                                                                   |

|-----------|---------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UM7108A/B | UM7108F | Designation | Description                                                                                                                                                                                                  |

|           | 39      | EOC         | End of conversion indicator. When each conversion ends, this pin will generate a positive pulse. Normally, use this signal to interrupt microcontroller                                                      |

| 26        | 40      | V -         | Negative power supply voltage. Connected to negative terminal of 9V battery                                                                                                                                  |

| 27        | 41      | VINT        | Integrator output. Connect to integration capacitor                                                                                                                                                          |

| 28        | 42      | VBUFF       | Integration resistor connection. Use a 47K Ω resistor for 200.0 mV full-scale and a 470K Ω resistor for 2.000 V full-scale                                                                                   |

| 29        | 43      | CAZ         | Autozero capacitor connection. Use a $0.47\mu F$ capacitor for 200.0 mV full-scale, and a $0.047\mu F$ capacitor for 2.000 V full-scale                                                                      |

| 30        | 44      | Vin -       | The analog low input signal is connected to this pin                                                                                                                                                         |

| 31        | 45      | Vin+        | The analog high input signal is connected to this pin                                                                                                                                                        |

| 32        | 46      | ANA - COM   | This pin is primarily used to set the analog ground reference for battery operation or in systems where the input signal is referenced to the power supply                                                   |

| 33        | 47      | CREF -      | See pin 34                                                                                                                                                                                                   |

| 34        | 48      | CREF+       | A 0.1µF capacitor is used in most applications. If a large common-mode voltage exists and a 200 mV scale is used, a 1.0µF capacitor is recommended which will hold the rollover error to less than 0.5 count |

| 35        | 1       | VREF -      | See pin 36                                                                                                                                                                                                   |

| Pin I     | No.     | Desire etter  | <b>D</b> anadata.                                                                                                                                                                                            |

|-----------|---------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UM7108A/B | UM7108F | - Designation | Description                                                                                                                                                                                                  |

| 36        | 2       | VREF+         | This analog input is required to generate a full-scale output (1,999 counts).  Place 100 mV between pin 35 and pin 36 for 200.0 mV full-scale. Place 1.00 V between pin 35 and pin 36 for 2.000 V full-scale |

| 37        | 3       | TEST1(DGND)   | Lamp test. When connected to V+ all the segments will be turned on and readout should be 1888. It may also be used as an internal logical ground, nominally 4.7 V below the V+                               |

| 38        | 4       | OSC3          | RC oscillator connection                                                                                                                                                                                     |

| 39        | 5       | OSC2          | Crystal oscillator (input) connection                                                                                                                                                                        |

| 40        | 6       | OSC1          | Crystal oscillator (output) connection                                                                                                                                                                       |

### **Functional Description**

An input signal to be measured is applied to the integrating capacitance for a fixed time as determined by a clock counter. The accumulated charge will be proportional to the input signal, for a fixed clock rate and constant current. The resulting integral is returned to zero by integrating a reference signal of polarity opposite that of the input signal. The length of time required for the integrator to return to zero, as measured with the clock counter to display at output, is proportional

to the average magnitude of the input signal over the integration period.

#### A. Analog Section

Fig. 1 shows the block diagram of the Analog Section for UM7108.

Each measurement cycle is divided into three parts.

These are: (1) Auto-zero [AZ]

- (2) Signal integration [INT]

- (3) Deintegration [DE]

Figure 1. UM7108 Analog Section

#### 1. Auto Zero Phase

During Auto-Zero, three things happen:

- (1) V<sub>IN+</sub> and V<sub>IN-</sub> are disconnected from pin 30 and 31 and shorted to ANA-COM

- (2) The reference capacitor is charged to the reference voltage.

- (3) A feedback loop is closed around the system to charge the auto-zero capacitor Caz to compensate for offset voltages in the buffer amplifier, integrator and comparator.

### 2. Signal Integrate Phase

During signal integration, the auto-zero loop is opened, the internal short circuit is removed, and the internal inputs high and low are connected to the external pins. The converter then integrates the differential voltage between VIN- and VIN+ for a fixed time (1000 counts). At the end of this phase, the polarity of the integrated signal is determined.

#### 3. De-Integrate Phase

The final phase is de-integration, or reference integration. VIN- is internally connected to ANA-COM and VIN+ is connected across the previously charged reference capacitor. Circuitry within the chip ensures that the capacitor will be connected with the correct polarity to cause the integrator output to return to zero. The time required to return to zero is proportional to the input signal. Specifically, the digital reading displayed is 1000 ( AIN VREE ).

#### 4. Component Value Selection:

#### Integrating Resistor ( RINT )

The buffer amplifier and integrator are designed with class A output stages with 100  $\mu$ A of quiescent current each. They can supply 20  $\mu$ A drive current with negligible linearity errors. RINT should be large enough to remain in linear region but small enough to reduce the leakage current on the PC board. For 200.0mV full scale, RINT is 47KQ; at 2.000 Volt full scale a 470KQ RINT is needed.

### Integrating Capacitor ( CINT )

CINT should be chosen to give the maximum voltage swing without causing the saturation of integrator output swing. According to the superior temperature coefficient — 20ppm/°C of analog common, analog common will be normally used as the differential voltage reference. It is fine for a nominal ±2.000V full scale integrator output swing. For 2 1/2 readings/ second (40 KHz clock), a 0.22µF capacitor is suggested. If a different oscillator frequency is used, CINT must be changed in inverse proportion to maintain the nominal ±2.000V full scale integrator output swing.

An additional requirement of RINT is that CINT must have low dielectric absorption to minimize rollover error. Polypropylene capacitors give undetectable errors at reasonable cost.

#### Reference Voltage Capacitor ( CREF )

The reference voltage used to ramp the integrator output voltage back to zero during the reference integrate cycle is stored on CREF. A  $0.1\mu F$  capacitor gives good performance when VIN- is tied to analog common. If a large analog common voltage exists VREF- unequal analog common) and a 200.0mV scale is used, a larger value is required to prevent rollover error

Generally 1.0µF will hold the rollover error to 0.5 count. In this case a mylar type dielectric capacitor is adequate.

#### Auto-Zero Capacitor ( CAZ )

The CAZ value has some influence on system noise. The following combination is recommended:

| Application        | Adequate Caz |

|--------------------|--------------|

| 200.0mV Full Scale | 0.47μF       |

| 2.000V Full Scale  | 0.047µF      |

It is better to use a mylar type capacitor to implement CAZ.

#### Oscillator Components ( Rosc, Cosc )

While using RC oscillator, the Rosc (between pin 39 and pin 40) should be  $100 \text{K}\Omega$  and Cosc is selected from the following equation:

Fosc =

$$\frac{0.45}{\text{Rosc} \times \text{Cosc}}$$

(Rosc in Ma, Cosc in  $\mu$ F)

#### Reference Voltage Selection

The analog input required to generate full scale output (2000 counts) is VIN = 2 VREF, thus:

| Required Full Scale Voltage | VREF    |

|-----------------------------|---------|

| 200.0mV                     | 100.0mV |

| 2.000V                      | 1.000V  |

However, in many applications where the A/D converter is connected to a transducer, there may exist a non-unity scale factor between the input voltage and the digital readout. For instance, a pressure transducer output is 400mV for 2000 lb/in, rather than dividing the input voltage by two, the VREF should be set to 200.0mV, then permit the transducer input to be used directly.

The differential voltage reference can also be used when a digital zero readout is required when Vin is not zero. This case is common in temperature measuring instrumentation. A compensating offset voltage can be applied between analog common and Vin and the transducer output is connected between Vin and analog common.

#### B. Digital Section

In the UM7108, the internal digital ground is generated from a 6.2 Volt Zener diode and a large p-channel follower. This supply is made stiff to absorb the relatively large capacitive current when the back plane (BP) is switched. The BP frequency is the clock frequency divided by 240. The segments are driven at the same frequency and amplitude and are in phase with BP when OFF, but out of phase when ON. In all cases, negligible DC voltage exists across the segments.

#### 1. System Timing

The oscillator frequency is divided by four before it clocks the decade counters. It is then further divided to form the three convert-cycle phase. These are signal integrate (1000 counts), reference deintegrate (0 to 2000 counts) and auto-zero (1000 to 3000 counts). For signals less than full scale, auto-zero gets the unused portion of reference deintegrate. This makes complete measure cycles of 4000 (16000 clock pulses) independent of input voltage. \* As a matter of fact, the total measurement cycle is 4001 counts for measured values less than 2000 counts. The measurement cycle becomes 4000 counts for over-flowmeasurement.

#### 2. Clock Circuit

UM7108A/B/F can use the following three clocking methods:

- 1. An external oscillator connected to OSC1 PIN.

- 2. A crystal between OSC2 PIN and OSC1 PIN.

- An RC oscillator using all three pins (OSC3, OSC2 & OSC1).

To achieve maximum rejection of 50/60 Hz pick up, the signal integrate cycle should be a multiple of 50/60 Hz, the following table describes the selection of oscillator frequencies for 50 or 60 Hz respectively.

|       | Oscillator Frequencies                 |

|-------|----------------------------------------|

| 50 Hz | *40 KHz, 50 KHz, 66 Exgmt KHz, 100 KHz |

| 60 Hz | *33 1/3 KHz, 40 KHz, 48 KHz, 60 KHz,   |

|       | 80 KHz, 100 KHz                        |

Note that 40 KHz (2.5 readings/second) will reject both 50 and 60 Hz line noise.

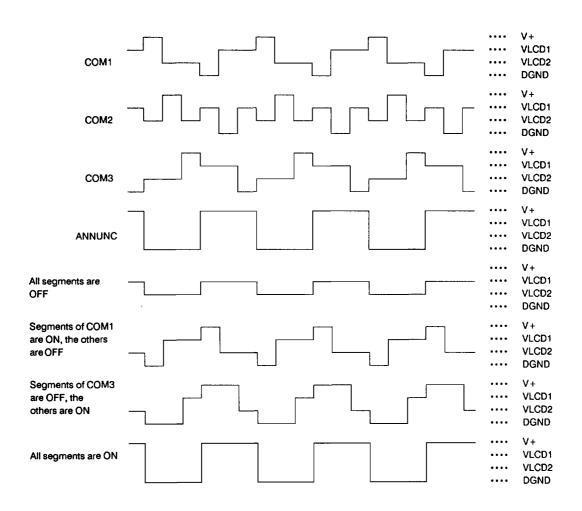

#### 3. LCD Display

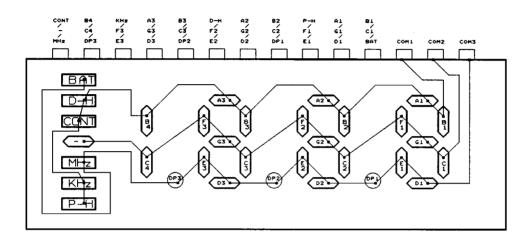

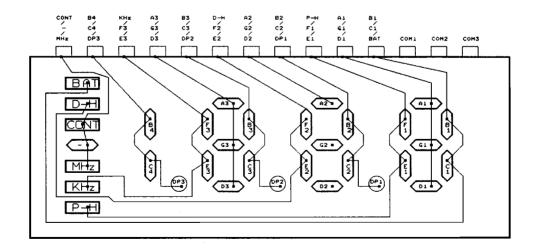

The UM7108A/B/F drives a triplex LCD with three commons. This LCD includes 31/2-digits, three decimal point polarity sign and annunciators for peakhold, data-hold, continuity, frequency and low battery. The following figure indicates the assignments of the display segments to the common and segment drive lines.

| UM7108A/B<br>Pin No. | UM7108F<br>Pin No. | COM1  | COM2 | сомз |

|----------------------|--------------------|-------|------|------|

| 2                    | 10                 | CONT  | -    | MHz  |

| 3                    | 11                 | B4    | C4   | DP3  |

| 4                    | 12                 | KHz   | F3   | E3   |

| 5                    | 13                 | A3    | G3   | D3   |

| 6                    | 14                 | В3    | С3   | DP2  |

| 7                    | 15                 | D – H | F2   | E2   |

| 8                    | 16                 | A2    | G2   | D2   |

| 9                    | 17                 | B2    | C2   | DP1  |

| 10                   | 18                 | P - H | F1   | E1   |

| 11                   | 19                 | A1    | G1   | D1   |

| 12                   | 20                 | B1    | C1   | BAT  |

| 13                   | 21                 | COM1  | -    |      |

| 14                   | 22                 | -     | COM2 | _    |

| 15                   | 23                 | _     | -    | СОМЗ |

The LCD common drive frequency is obtained by dividing the oscillator frequency (Fclock) by 240.

$$Flcd = \frac{Fclock}{240}$$

#### The LCD waveform is as follows :

The annunciator output is a square wave running at the LCD backplane frequency (ex. 167 Hz for Fclock = 40 KHz). The pk-pk amplitude is equal to (V+

- DGND). Connecting an annunciator of the LCD to the ANNUNC pin turns the annunciator on; connecting it to its common turns it off.

# UM7108A/B/F LCD COMMON LAYOUT

# UM7108A/B/F LCD SEGMENT LAYOUT

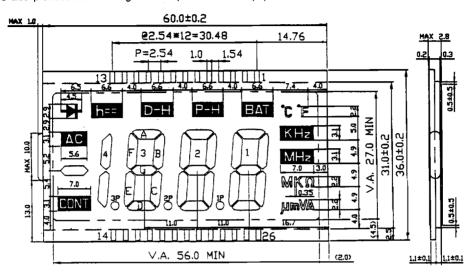

UMC also provides the following LCD sample for UM7108A/B/F to achieve full features

# Viewing Direction

Notes: 1. Display Type

2. Viewing Direction

Polarizer Mode

4. Drive Method

5. Operating Voltage

5. Operating voltage

6. Operating Temp

7. Storage Temp

8. Connector

Twisted Nematic Display

6 O'Clock

Reflective/Positive

1/3 Duty 1/3 Bias

1/3 Duty 1/3 Dia

5.0V

-10°C ~ +60°C

-20°C ~ +70°C

Zebra

| PIN  | 1    | 2    | 3    | 4   | 5  | 6   | 7  | 8  | 9   | 10         | 11 | 12  | 13 |

|------|------|------|------|-----|----|-----|----|----|-----|------------|----|-----|----|

| сомз | сомз | /    | 1    | BAT | 1D | 1E  | 1P | 2D | 2E  | 2 <b>P</b> | 3D | 3E  | 3P |

| СОМ2 | /    | СОМ2 | /    | 1C  | 1G | 1F  | 2C | 2G | 2F  | зС         | 3G | 3F  | 4C |

| сом1 | /    | /    | COM1 | 1B  | 1A | Р-Н | 2B | 2A | D-H | 3B         | зА | KHz | 4B |

| PIN  | 14  | 15 | 16 | 17   | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 |

|------|-----|----|----|------|----|----|----|----|----|----|----|----|----|

| сомз | /   | /  | /  | MHz  | 1  | /  | /  | /  | /  | /  | /  | /  | 1  |

| COM2 | /   | /  | /  |      | /  | /  | /  | /  | /  | /  | /  | /  | 1  |

| COM1 | hFE |    | AC | CONT | М  | K  | Ω  | μ  | m  | V  | Α  | ٠c | ۰F |

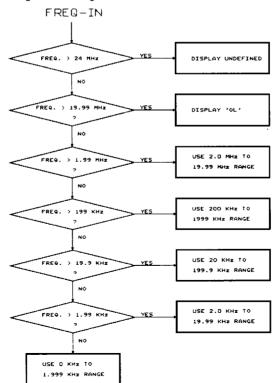

#### 4. Frequency Counter

In addition to serving as an analog-to-digital converter, the UM7108F also provides 2 KHz to 20 MHz five decade auto-range frequency counter. In the counter mode, pulses at the FREQ-IN will be counted and displayed.

The UM7108F frequency counter derives its time base from the clock oscillator and gets one readout per

second. The frequency counter accuracy is determined by the oscillator accuracy. For accurate frequency measurement, a 40 KHz quartz crystal oscillator is recommended.

The decimal points are automatically set in frequency mode, the following table indicates the auto-range decimal points and annunciator selection versus frequency counter input (Fin).

| FREQ-IN              | Decimal Point | Annunciator |

|----------------------|---------------|-------------|

| 0 KHz to 1.999 KHz   | DP3           | KHz         |

| 2.0 KHz to 19.99 KHz | DP2           | KHz         |

| 20 KHz to 199.9 KHz  | DP1           | KHz         |

| 200 KHz to 1999 KHz  | NONE          | KHz         |

| 2.0 MHz to 19.99 MHz | DP2           | MHz         |

Auto-Range Frequency Counter Range Selection Algorithm

D14 D15 Decimal Point

None

DP1 DP2 DP3

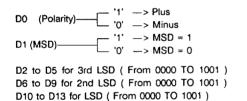

#### 5. Serial Data Output

In addition to the LCD output, the UM7108F provides serial data output for use in connection with microcontrollers. During this operation, UM7108F uses CLK, SDO and EOC pins. The following is the timing description of this connection.

The EOC pin will rise HIGH at the end of conversion and the content of serial output data buffer will update simultaneously.

The waveform of EOC pin will go LOW as soon as CLK pin receives clock signal. Otherwise the EOC pin will stay HIGH and then go LOW in 10 ms.

### Serial Data Output Format

| D15     | D14  | D13 | D12  | D11 | D10 | D9  | D8  | D7    | D6  | D5  | D4    | DЗ    | D2  | D1 | Dρ  | > Out    |

|---------|------|-----|------|-----|-----|-----|-----|-------|-----|-----|-------|-------|-----|----|-----|----------|

| Decima  | al   | LSB |      |     | MSB | LSB |     |       | MSB | LSB |       |       | MSB | M  | L 1 | Polarity |

| Point B | 3its |     |      |     |     |     |     |       |     |     |       |       |     | S  |     |          |

|         |      |     | — LS | יחי |     |     | 20  | d LSD |     |     | 3rd   | LSD - |     | ם  |     |          |

|         |      |     | — L3 | · - | -   |     | 211 | U LOD |     |     | - 51G | LOD . |     | 1  |     |          |

D14 & D15 for

Decimal Point Bits

#### 1. Voltage Mode:

#### 2. Frequency Mode:

The rest are same as voltage mode.

### **Special Data Format**

| Items                         | D15D6            | D5 | D4 | <b>D</b> 3 | <b>D</b> 2 | D1 | DO |

|-------------------------------|------------------|----|----|------------|------------|----|----|

| (1) Initial State ( 0000)     | Random and don't | 1  | 1  | 1          | 1          | 1  | 1  |

| (2) Positive Overflow ( OL)   | care             | 0  | 0  | 1          | 1          | 1  | 1  |

| (3) Negative Overflow ( - OL) |                  | 0  | 0  | 1          | 1          | 1  | 0  |

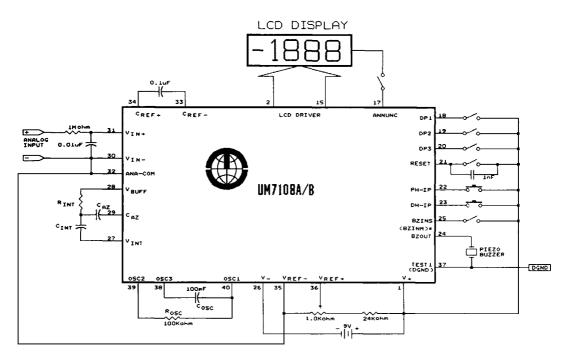

# Application Circuits (for reference only)

### (1) For UM7108A/B

| Component | Nominal Full-Scale Voltage |         |  |  |  |  |  |

|-----------|----------------------------|---------|--|--|--|--|--|

| Value     | 2.000V                     | 200.0mV |  |  |  |  |  |

| Caz       | 0.047μF                    | 0.47μF  |  |  |  |  |  |

| RINT      | 470ΚΩ                      | 47K Ω   |  |  |  |  |  |

| CINT      | 0.22µF                     | 0.22µF  |  |  |  |  |  |

| VREF      | 1.000V                     | 100.0mV |  |  |  |  |  |

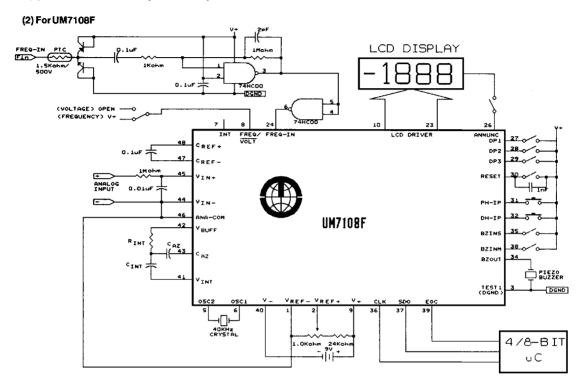

# **Application Circuits (continued)**

| Component | Nominal Full-Sca | Nominal Full-Scale Voltage |  |  |  |  |  |  |  |

|-----------|------------------|----------------------------|--|--|--|--|--|--|--|

| Value     | 2.000V           | 200.0mV                    |  |  |  |  |  |  |  |

| Caz       | 0.047µF          | 0.47μF                     |  |  |  |  |  |  |  |

| RINT      | 470ΚΩ            | 47KΩ                       |  |  |  |  |  |  |  |

| CINT      | 0.22µF           | 0.22µF                     |  |  |  |  |  |  |  |

| VREF      | 1.000V           | 100.0mV                    |  |  |  |  |  |  |  |

# **Ordering Information**

| Part No. | Buzzer Input Selection | Package |

|----------|------------------------|---------|

| UM7108A  | BZINS                  | 40L DIP |

| UM7108B  | BZINM                  | 40L DIP |

| UM7108F  | BZINS, BZINM           | 48L QFP |