#### LogicGreen Technologies Co., LTD

#### Functional Overview

#### z High performance and low power consumption 8 Bit LGT8XMKernel

#### z advanced RISC Framework

131 Instructions,80%The above is a single cycle execution

32x8 General working register

32MHz Up to when working 32MIPS Execution efficiency

Internal single cycle multiplier (8x8)

#### z Non-volatile program and data storage space

32Kbytes On-chip online programming FLASH Program memory

#### 2Kbytes Internal data SRAM

Programmable E2PROMAnalog interface, support byte access

Brand new program encryption algorithm to ensure user code security

#### z Peripheral Controller

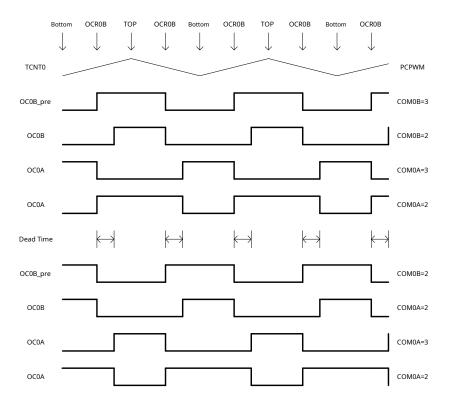

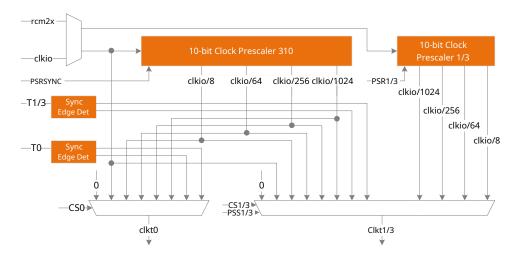

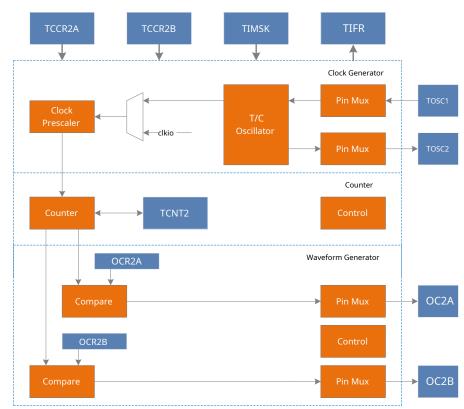

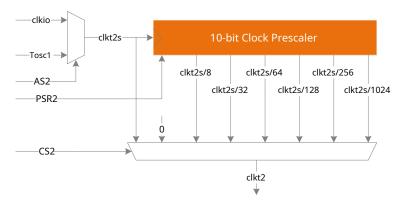

Two with independent prescaler 8 Bit timer, support compare output mode

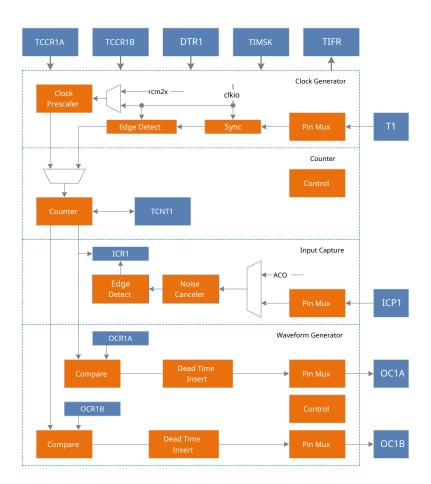

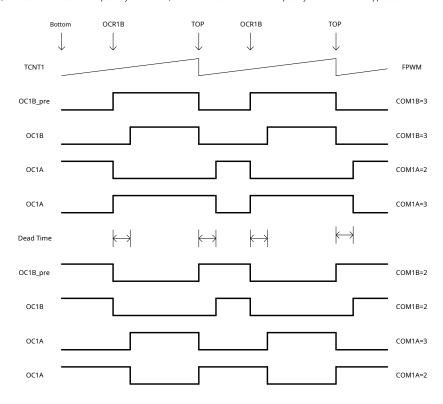

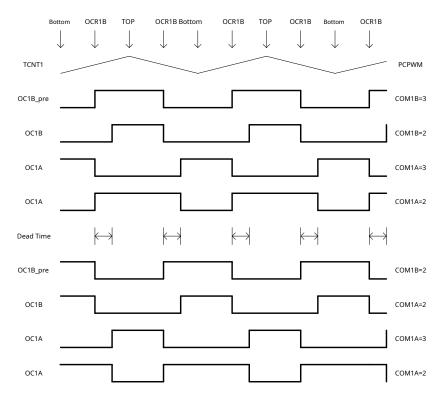

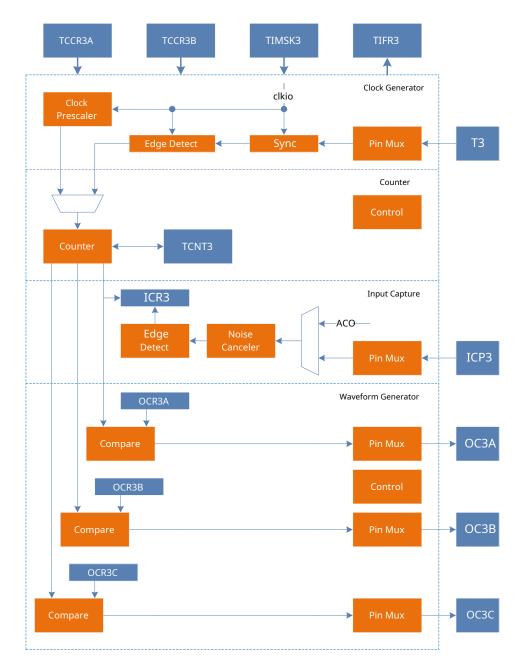

Two with independent prescaler 16 Bit timer, support input capture and compare output

internal 32KHz Can be calibrated **RC** Oscillator realizes real-time counter function

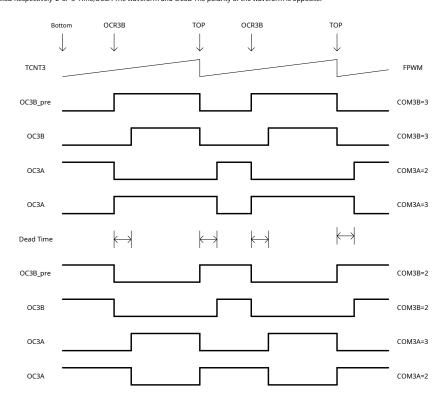

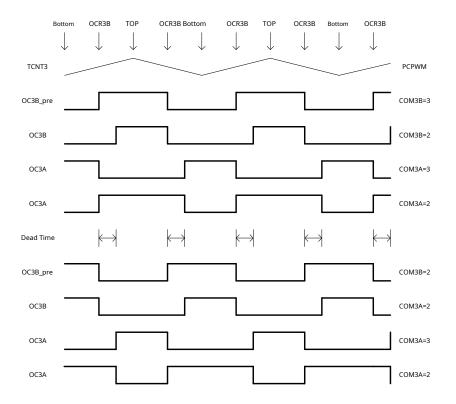

Can support up to 9 road PWMOutput, three groups of complementary programmable dead zone control

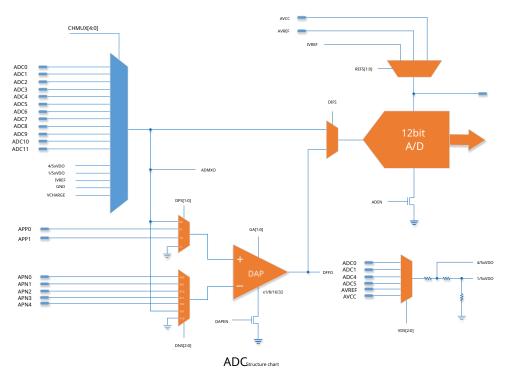

12 aisle 12 Bit high-speed analog-to-digital converter (ADC)

- Optional internal and external reference voltage

- Programmable gain (X1/8/16/32)Differential amplifier input channel

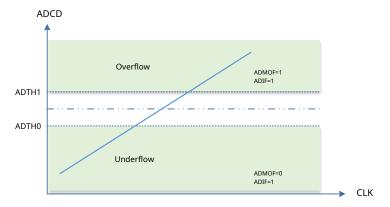

- automatic threshold voltage monitoring mode

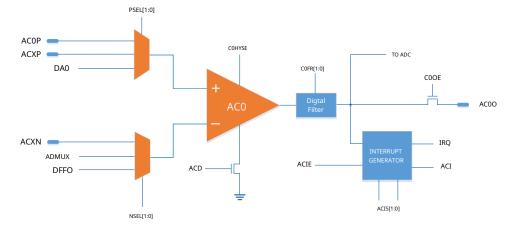

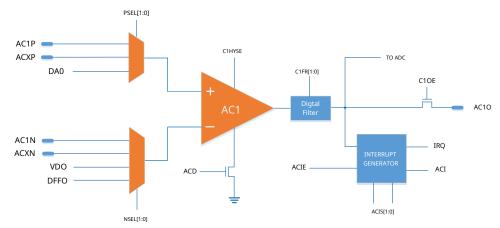

Two analog comparators (AC), Support comes from ADC Expansion of input channels

internal 1.024V/2.048V/4.096V  $\pm 1\%$ Calibrable reference voltage source

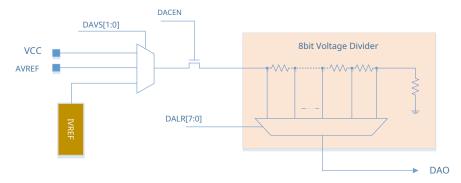

One 8 Bit programmable **DAC**, Can be used to generate a reference voltage

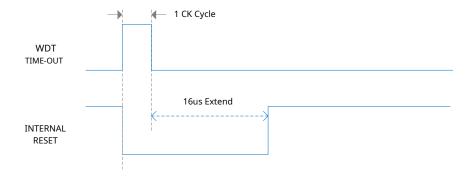

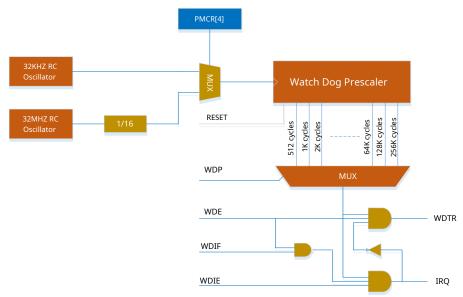

source programmable watchdog timer (WDT)

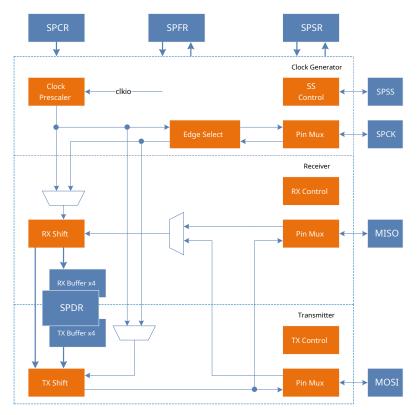

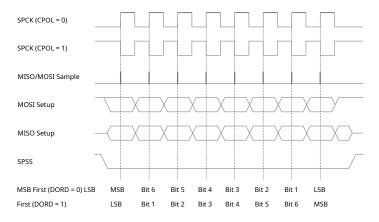

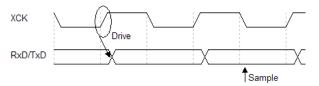

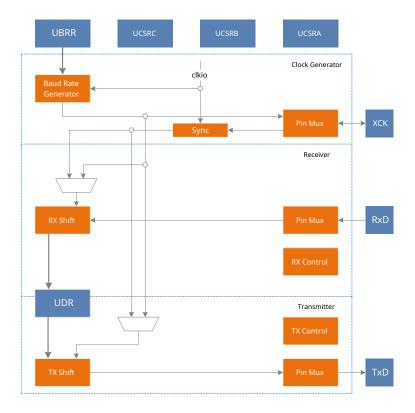

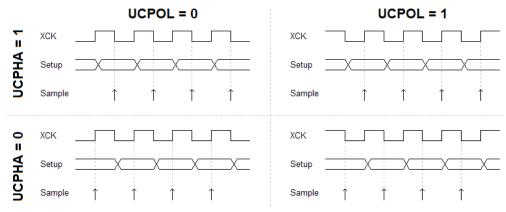

$Programmable \ synchronous/asynchronous \ serial \ interface \ (\textbf{USART/SPI})$

Synchronous Peripheral Interface (SPI), Programmable master/slave working

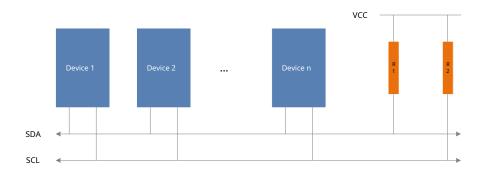

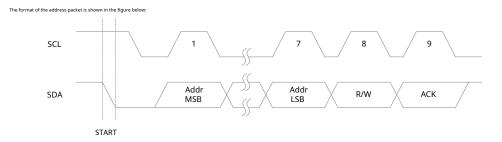

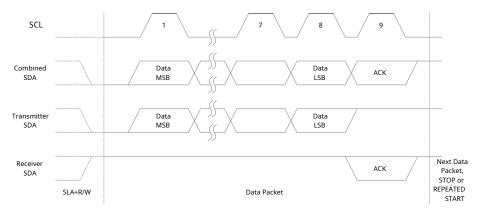

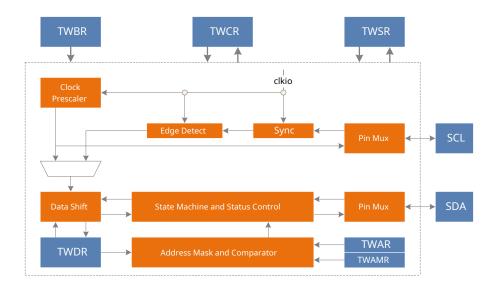

mode two-wire serial interface (TWI), compatible I2C Master-slave mode

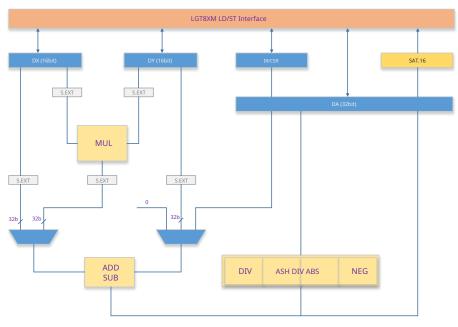

16 Bit digital operation acceleration unit (DSC), Supports direct 16 Bit data access

#### z Special processor function

SWD Two-wire on-chip debugging/mass production interface

External interrupt source and I/O Interrupt-on-change support

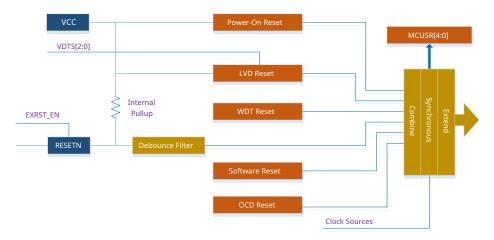

$Built-in\ power-on\ reset\ circuit\ (\textbf{POR})\ And\ programmable\ low-voltage\ detection\ circuit\ (\textbf{LVD})\ Built-in\ power-on\ reset\ circuit\ (\textbf{LVD})\ Buil$

in 1%Can be calibrated 32MHz RC Oscillator, support frequency multiplication output built-in 1% Can be calibrated 32KHz RC Oscillator external support 32.768KHz as well as 400K-32MHz

can be cambrated 521112 the obtained external support 5217 contribute as near as 10011 5211111

Crystal input

6x High current push-pull drive IO, Support high speed PWMapplication

# Logic reen

# 8-bit LGT8XM

RISC Microcontroller with In-System Programmable FLASH Memory

*LGT8F88P LGT8F168P*

LGT8F328P

Data book Version 1.0.5

Application field

Home appliances

Motor drive

Automatic control

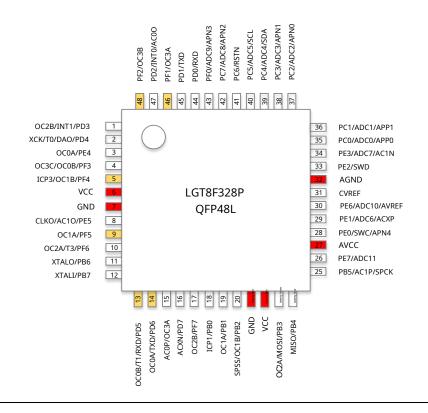

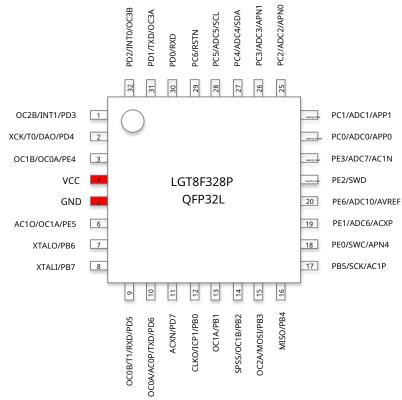

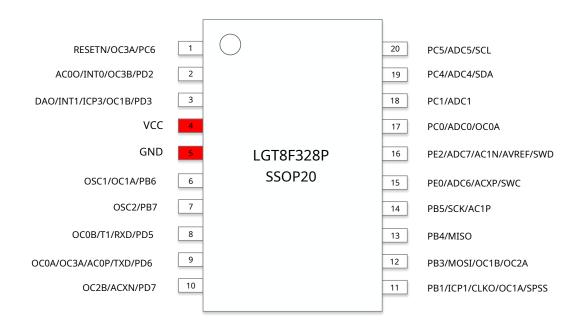

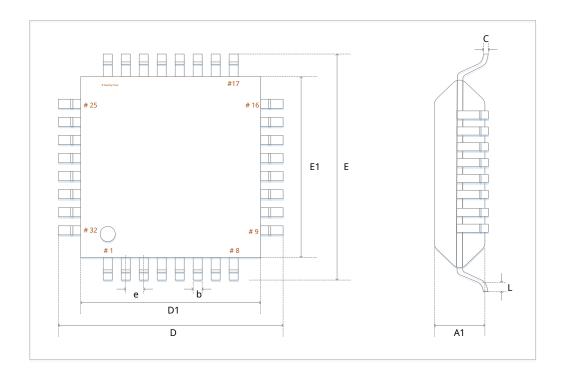

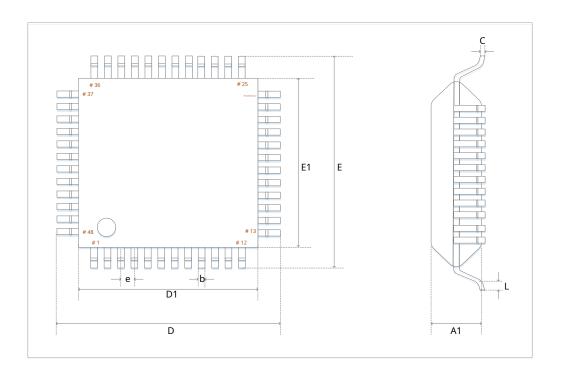

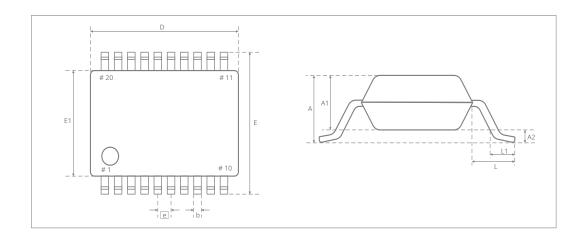

z I/O And package:QFP48/32L, SSOP20L

z Lowest power consumption: 1uA@3.3V

#### z working environment

Operating Voltage:  $1.8V \sim 5.5V$  working frequency:  $0 \sim 32MHz$  Operating temperature: -40C

~ +85C HBM ESD:> 4KV

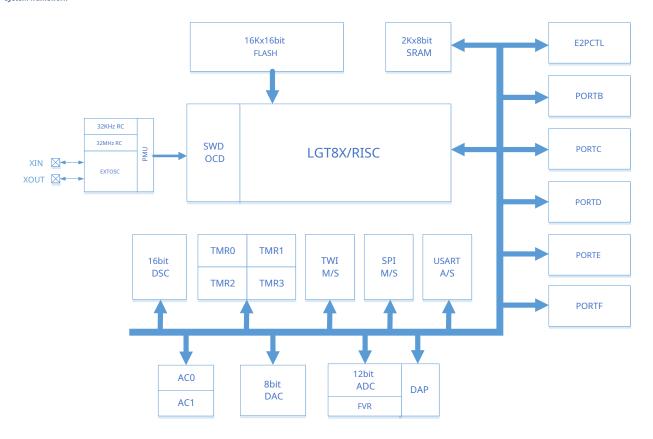

# system framework

| Module name   | Module function                                                                                                        |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SWD           | Debug module, at the same time realize online debugging and ISP Features                                               |  |  |  |

| LGT8X         | 8bit high performance RISC Kernel data                                                                                 |  |  |  |

| E2PCTL        | FLASH Access interface controller                                                                                      |  |  |  |

| PMU           | Power consumption management module, responsible for managing the transition between the working states of the system. |  |  |  |

| PORTB/C/D/E/F | Universal programmable input and output ports                                                                          |  |  |  |

| DSC           | 16 Bit digital operation acceleration unit                                                                             |  |  |  |

| ADC           | 8 aisle 12 Bit analog to digital converter                                                                             |  |  |  |

| DAP           | Programmable gain differential amplifier                                                                               |  |  |  |

| IVREF         | 1.024V/2.048V/4.096V Internal reference                                                                                |  |  |  |

| AC0/1         | analog comparator                                                                                                      |  |  |  |

| TMR0/1/2/3    | 8/16 Bit timer/counter,PWMController                                                                                   |  |  |  |

| WDT           | watchdog reset module                                                                                                  |  |  |  |

| SPI M/S       | Master-slave SPI Controller                                                                                            |  |  |  |

| TWI M/S       | Master-slave two-wire interface controller, compatible I2C protocol                                                    |  |  |  |

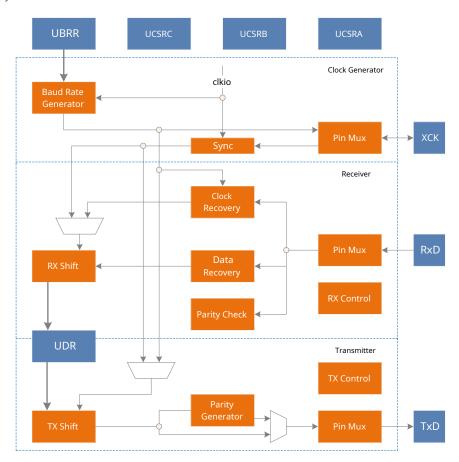

| USART         | Synchronous/asynchronous serial transceiver                                                                            |  |  |  |

| DAC           | 8 Digital-to-analog converter                                                                                          |  |  |  |

#### Package definition

# Pin description

LGT8FX8P In the series package,QFP48L The package leads to all pins. Other packages are inQFP48 Multiple internal I/O Generated by binding to a pin. Pay special attention when configuring the pin direction. The following table lists the binding of various package pins:

| QFP48 | QFP32 | SSOP20 | Function Description                      |

|-------|-------|--------|-------------------------------------------|

|       |       |        | PD3/INT1/OC2B*                            |

| 04    | 04    |        | PD3: Programmable port D3                 |

| 01    | 01    |        | INT1: External interrupt input 1          |

|       |       |        | OC2B: Timer 2 Compare match output B      |

|       |       | 03     | PD4/DAO/T0/XCK                            |

|       |       |        | PD4: Programmable port D4                 |

| 02    | 02    |        | DAO: internal DAC Output                  |

|       |       |        | T0: Timer0 External clock input           |

|       |       |        | XCK: USART Synchronous transmission clock |

|       |       |        | PE4/0C0A*                                 |

| 03    | 03    | -      | PE4: Programmable port E4                 |

|       |       |        | OC0A: Timer 0 Compare match output A      |

|       |       |        | PF3/OC3C/OC0B*                            |

| 04    |       |        | PF3: Programmable port F3                 |

| 04    | -     | -      | OC3C: Timer 3 Compare match output C      |

|       |       |        | OC0B: Timer 0 Compare match output B      |

|       |       |        | PF4/OC1B*/ICP3                            |

| 05    | 02    |        | PF4: Programmable port F4                 |

| 05    | 03    | 03     | OC1B: Timer 1 Compare match output        |

|       |       |        | B ICP3: Timer 3 Capture input             |

| 06    | 04    | 04     | VCC                                       |

| 07    | 05    | 05     | GND                                       |

|       |       |        | PE5/AC1O/CLKO*                            |

| 00    |       |        | PE5: Programmable port E5                 |

| 08    |       | -      | C1O: Analog comparator AC1 Output         |

|       | 06    |        | CLKO: System clock output                 |

|       |       |        | PF5/OC1A*                                 |

| 09    |       | 06     | PF5: Programmable port F5                 |

|       |       |        | OC1A: Timer 1 Compare match output        |

|       |       |        | A PF6/T3/OC2A*                            |

| 10    | _     |        | PF6: Programmable port F6                 |

| 10    | -     | _      | T3: Timer 3 External clock input          |

|       |       |        | OC2A: Timer 2 Compare match output        |

|       |       |        | A PB6/XTALO                               |

| 11    | 07    | 06     | PB6: Programmable port B6                 |

|       |       |        | XTALO: Crystal oscillator IO Output port  |

|            | 08             | 07 | PB7/XTALI                                         |

|------------|----------------|----|---------------------------------------------------|

| 12         |                |    | PB7: Programmable port B7` XTALI:                 |

|            |                |    | Crystal oscillator IO Input port                  |

|            |                |    | PD5/RXD*/T1/OC0B                                  |

|            |                |    | PD5: Programmable port D5                         |

| 13         | 09             | 80 | RXD: USART Data reception (optional)              |

|            |                |    | T1: Timer 1 External clock input                  |

|            |                |    | OCOB: Timer 0 Compare match output                |

|            |                |    | B PD6/TXD*/OC0A                                   |

| 14         |                |    | PD6: Programmable port D6                         |

| 17         |                |    | TXD: USART Data transmission (optional)           |

|            | 10             | 09 | OC0A: Timer 0 Compare match output                |

|            |                |    | A ACOP/0C3A                                       |

| 15         |                |    | AC0P: Analog comparator 0 Positive input          |

|            |                |    | OC3A: Timer 3 Compare match output                |

|            |                |    | A PD7/ACXN                                        |

| 16         | 11             |    | PD7: Programmable port D7                         |

|            |                | 10 | ACXN: Analog comparator 0/1 Common negative input |

|            |                | 10 | PF7/OC2B                                          |

| 17         | -              |    | PF7: Programmable port F7                         |

|            |                |    | OC2B: Timer 2 Compare match output                |

|            |                |    | B PB0/ICP1                                        |

| 18         | 12             |    | PB0: Programmable port B0                         |

|            |                | 11 | ICP1: Timer 1 Capture input                       |

|            |                |    | PB1/OC1A                                          |

| 19         | 13             |    | PB1: Programmable port B1                         |

|            |                |    | OC1A: Timer 1 Compare match output                |

|            |                |    | A PB2/OC1B/SPSS                                   |

| 20         | 14             | 12 | PB2: Programmable port B2                         |

|            |                |    | OC1B: Timer 1 Compare match output B              |

|            |                |    | SPSS: SPI Slave mode chip select                  |

| twenty one | -              | -  | GND                                               |

| twenty two | , <b>-</b>     | -  | VCC                                               |

|            |                |    | PB3/MOSI/OC2A                                     |

| twenty thr | <sub></sub> 15 | 12 | PB3: Programmable port B3                         |

| twenty tin |                |    | MOSI: SPI Host output/Slave input                 |

|            |                |    | OC2A: Timer 2 Compare match output                |

|            |                |    | A PB4/MISO                                        |

| twenty fou | , <b>16</b>    | 13 | PB4: Programmable port B4                         |

|            |                |    | MISO: SPI Host input/Slave output                 |

|            |                |    | PB5/SPCK/AC1P                                     |

| 25         | 17             | 14 | PB5: Programmable port B5                         |

|            | .,             |    | SPCK: SPI Clock signal                            |

|            |                |    | AC1P: Analog comparator 1 Positive input          |

|            |            |         | PE7/ADC11                                            |

|------------|------------|---------|------------------------------------------------------|

| 26         | _          | _       | PE7: Programmable port E7                            |

|            |            |         | ADC11: ADC Analog input channel 11 AVCC:             |

| 27         | -          | -       | Internal analog circuit power supply                 |

|            |            |         | PE0/SWC/APN4                                         |

|            | 4.0        |         | PE0: Programmable port E0                            |

| 28         | 18         |         | SWC: SWD Debug interface clock                       |

|            |            | 45      | APN4: Differential amplifier reverse input channel 4 |

|            |            | 15      | PE1/ADC6/ACXP                                        |

| 20         | 40         |         | PE1: Programmable port E1                            |

| 29         | 19         |         | ADC6: ADC Analog input channel 6 ACXP: Analog        |

|            |            |         | comparator 0/1 Common positive input                 |

|            |            |         | PE6/ADC10/AVREF                                      |

| 30         | 20         | 16      | PE6: Programmable port E6                            |

| 30         | 20         | 10      | ADC10: ADC Analog input channel 10                   |

|            |            |         | AVREF: ADC External reference input                  |

| 31         |            |         | CVREF: ADC Reference voltage output                  |

| 31         | -          | -       | Only for external 0.1uF Filter capacitor             |

| 32         | -          | -       | AGND: Internal analog circuit ground                 |

|            |            |         | PE2/SWD                                              |

| 33         | twenty on  | e       | PE2: Programmable port E2                            |

|            |            |         | SWD: SWD Debug interface data line                   |

|            |            | 16      | PE3/ADC7/AC1N                                        |

| 34         |            |         | PE3: Programmable port E3                            |

| <b>3</b> 7 | twenty tw  | wb      | ADC7: ADC Analog input channel 7                     |

|            |            |         | AC1N: Analog comparator negative input               |

|            |            |         | PC0/ADC0/APP0                                        |

| 35         |            | ee 17   | PC0: Programmable port C0                            |

| 33         | twenty thi | ree I / | ADC0: ADC Analog input channel 0 APP0:               |

|            |            |         | Differential amplifier forward input channel 0       |

|            |            |         | PC1/ADC1/APP1                                        |

| 36         | twenty for | , 18    | PC1: Programmable port C1                            |

|            | twenty for |         | ADC1: ADC Analog input channel 1 APP1:               |

|            |            |         | Differential amplifier forward input channel 1       |

|            |            |         | PC2/ADC2/APN0                                        |

| 37         | 25         | _       | PC2: Programmable port C2                            |

|            | 23         | _       | ADC2: ADC Analog input channel 2 APN0:               |

|            |            |         | Differential amplifier reverse input channel 0       |

|            |            |         | PC3/ADC3/APN1                                        |

| 38         | 26         | 26 -    | PC3: Programmable port C3                            |

| 30         | 20         |         | ADC3: ADC Analog input channel 3 APN1:               |

|            |            |         | Differential amplifier reverse input channel 1       |

|    |    | 19 | PC4/ADC4/SDA                                   |

|----|----|----|------------------------------------------------|

|    |    |    | PC4: Programmable port C4                      |

| 39 | 27 |    | ADC4: ADC Analog input channel 4               |

|    |    |    | SDA: I2C Controller data line                  |

|    |    |    | PC5/ADC5/SCL                                   |

|    |    |    | PC5: Programmable port C5                      |

| 40 | 28 | 20 | ADC5: ADC Analog input channel 5               |

|    |    |    | SCL: I2C Controller clock line                 |

|    |    |    | PC6/RESETN                                     |

| 41 | 29 | 1  | PC6: Programmable port C6                      |

|    |    |    | RESETN: External reset input                   |

|    |    |    | PC7/ADC8/APN2                                  |

| 42 |    |    | PC7: Programmable port C7                      |

| 42 | -  | -  | ADC8: ADC Analog input channel 8 APN2:         |

|    |    |    | Differential amplifier reverse input channel 2 |

|    |    |    | PF0/ADC9/APN3                                  |

| 42 |    |    | PF0: Programmable port F0                      |

| 43 | -  | -  | ADC9: ADC Analog input channel 9 APN3:         |

|    |    |    | Differential amplifier reverse input channel 3 |

|    |    |    | PD0/RXD                                        |

| 44 | 30 | -  | PD0: Programmable port D0                      |

|    |    |    | RXD: USART Data receiving input                |

|    |    |    | PD1/TXD                                        |

| 45 |    | -  | PD1: Programmable port D1                      |

|    | 31 |    | TXD: USART Data transmission output            |

|    | 31 |    | PF1/OC3A                                       |

| 46 |    | 1  | PF1: Programmable port F1                      |

|    |    |    | OC3A: Timer 3 Compare match output             |

|    |    |    | A PD2/INT0/AC0O                                |

| 47 |    |    | PD2: Programmable port D2                      |

| 47 |    |    | INTO: External interrupt input 0               |

|    | 32 | 2  | AC00: Analog comparison 0 Output               |

|    |    |    | PF2/OC3B                                       |

| 48 |    |    | PF2: Programmable port F2                      |

|    |    |    | OC3B: Timer 3 Compare match output B           |

#### LGT8XMKernel

- Z Low power design

- Z high efficiency RISC Framework

- Z 16 Bit LD/ST Extension(uDSU dedicated)

- Z 130 Instructions, of which 80%The above is a single-cycle

- Z embedded online debugging (OCD)stand by

#### Overview

This chapter mainly describes LGT8XM Kernel architecture and functions. Kernel isMCU The brain is responsible for ensuring the correct execution of the program, so the kernel must be able to accurately perform calculations, control peripherals, and handle various interrupts.

# Instruction **NPC** Buffer Generator Pipeline **Programmemory** Control Instruction & Pre-execute Register File Decode 16bit ALU 8bit 8bit 16bit uDSU 8/16bit SRAM

LGT8XMThe structure of the kernel

In order to achieve greater efficiency and parallelism,LGT8XM The kernel adopts the Haval architecture - Independent data and program bus.

Instructions are executed through an optimized two-stage pipeline. The two-stage pipeline can reduce the number of invalid instructions in the pipeline and reduce the number of FLASH Access to the program memory, so the power consumption of the kernel can be reduced. SimultaneouslyLGT8XMThe kernel adds an instruction cache in the pre-stage of fetching instructions (can be cached at the same time 2 Instructions), through the pre-execution module in the instruction fetch cycle, further reducing the FLASH Access frequency of program memory; after extensive testing,LGT8XM It can reduce about 50%Correct FLASH The access, greatly reducing the operating power consumption of the system.

LGT8XMThe kernel has 32 A 8 General-purpose working register for high-speed access (Register file), Which helps to realize single-cycle arithmetic and logic operations (ALU). In general, ALU Both operands of the operation come from the general working register, ALU

The result of the operation is also written into the register file in one cycle.

32 Through the working register 6 One is used to combine two to form three 16 Bit register, can be used for indirect addressing address pointer, used to access external storage space and FLASH Program space.LGT8XM Support single cycle 16 Bit arithmetic operations greatly improve the efficiency of indirect addressing.LGT8XMThese three special 16 The bit register is named X, Y, Z Register, will be introduced in detail later.

ALU Supports arithmetic and logic operations between registers and between constants and registers, and a single register can also be operated

in ALU Executed.ALU After the operation is completed, the effect of the operation result on the state of the core is updated to the status register (

SREG). Program flow control is realized by conditional and unconditional jump/call, which can be addressed to all program areas. most

LGT8XMThe instruction is 16 Bit. One for each program address space16 Bit or 32 Bit LGT8XMinstruction.

After the kernel responds to the interrupt or subroutine call, the return address (PC)Is stored in the stack. The stack is allocated in the general data of the systemSRAMMedium, so the size of the stack is only limited by the system SRAMThe size and usage. All applications that support interrupts or subroutine calls must first initialize the stack pointer register (SP),SP able to pass IO Space access. data

SRAM able to pass 5 A different addressing mode access.LGT8XM The internal storage space is linearly mapped to a unified address space. For details, please refer to the introduction in the storage chapter.

LGT8XM The core contains a flexible interrupt controller, the interrupt function can be controlled by a global interrupt enable bit in the status register. All interrupts have an independent interrupt vector. The priority of the interrupt has a corresponding relationship with the interrupt vector address. The smaller the interrupt address, the higher the priority of the interrupt.

I/O Space contains 64 Can pass IN/OUT The register space directly addressed by the instruction. These registers show the control and status registers of the core,SPI And other I/O Control functions of peripherals. This part of the space can passIN/OUT Instructions are directly accessed, or they can be accessed through their addresses mapped to the data memory space (0x20 - 0x5F). In addition, LGT8FX8P Also includes extended I/O Space, they are mapped to data storage space 0x60 - 0xFF, Can only be used here ST/STS/STD as well as LD/LDS/LDD Command access.

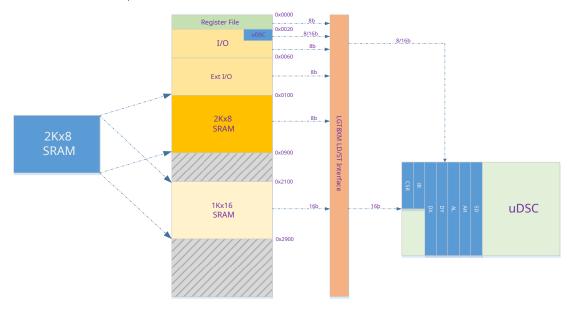

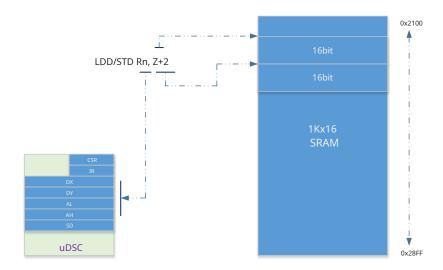

For enhancement LGT8XM The computing power of the kernel has been added to the popular line of instructions 16 Bit LD/ST Extension. this 16 Bit LD/ST Extension acceleration unit (uDSU)Work to achieve efficient 16 Bit data operations. At the same time, the kernel also addsRAM Spatial 16 Bit access capability. therefore 16 Bit LD/ST The extension can be in uDSU, RAM, And transfer between working registers 16 Bit data. For specific details, please refer to "Digital computing accelerator" chapter.

#### Arithmetic and logical operation unit (ALU)

LGT8XMContains a 16 Bit arithmetic logic operation unit can be completed in one cycle 16 Arithmetic operations for data. EfficientALU versus 32 Two general-purpose working registers are connected. The arithmetic logic operation between two registers or between the register and the immediate data can be completed in one cycle.ALU There are three types of operations: arithmetic, logic and bit operations. SimultaneouslyALU The part also includes a single-cycle hardware multiplier, which can achieve two 8 Direct signed or unsigned operations on bit registers. Please refer to the detailed introduction in the instruction set section.

#### Status register (SREG)

The status register mainly saves the execution Last time ALU The result information generated by the operation. This information is used Control program execution flow. The status register is in ALU Update after the operation is completely finished, so that the use of a separate comparison instruction can be omitted, and a more compact and efficient code implementation can be brought. The value of the status register is not automatically saved and restored when responding to the interrupt and exiting from the interrupt, which requires software to achieve.

#### **SREG Register definition**

|                | SREG System status register |                                                                                                                                                                                                                                                                    |                                                                                                                                                 |                                                                                                    |                                                              |                                                                 |                     |                    |

|----------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------|---------------------|--------------------|

| address: 0x3   | BF (0x5F)                   |                                                                                                                                                                                                                                                                    |                                                                                                                                                 | Defaults:                                                                                          | 0x00                                                         |                                                                 |                     |                    |

| Bit            | 7                           | 6                                                                                                                                                                                                                                                                  | 5                                                                                                                                               | 4                                                                                                  | 3                                                            | 2                                                               | 1                   | 0                  |

| Name           | I                           | Т                                                                                                                                                                                                                                                                  | Н                                                                                                                                               | S                                                                                                  | V                                                            | N                                                               | Z                   | С                  |

| R/W            | R/W                         | R/W                                                                                                                                                                                                                                                                | R/W                                                                                                                                             | R/W                                                                                                | R/W                                                          | R/W                                                             | R/W                 | R/W                |

| Bit definition |                             |                                                                                                                                                                                                                                                                    |                                                                                                                                                 |                                                                                                    |                                                              |                                                                 |                     |                    |

| [0]            | С                           | Carry flag, indic                                                                                                                                                                                                                                                  | ating that an arith                                                                                                                             | metic or logical op                                                                                | eration caused a c                                           | arry, please refer t                                            | o the instruction o | lescription for    |

| [1]            | Z                           | Zero flag, indica                                                                                                                                                                                                                                                  | ting that the resu                                                                                                                              | lt of arithmetic or lo                                                                             | ogic operation is z                                          | ero, please refer to                                            | the instruction de  | escription         |

| [2]            | N                           | Negative sign, wh                                                                                                                                                                                                                                                  | Negative sign, which means that arithmetic or logical operation produces a negative number, please refer to the instruction description section |                                                                                                    |                                                              |                                                                 |                     |                    |

| [3]            | V                           | Overflow flag, indicating that the result of the two's complement operation has overflowed, please refer to the instruction description section                                                                                                                    |                                                                                                                                                 |                                                                                                    |                                                              |                                                                 |                     |                    |

| [4]            | S                           | Sign bit, equivalent to N versus V The result of the exclusive OR operation, please refer to the instruction description section for details                                                                                                                       |                                                                                                                                                 |                                                                                                    |                                                              |                                                                 |                     |                    |

| [5]            | Н                           | Half-carry flag, in BCD Useful in calculations, representing the half-carry generated by byte operations                                                                                                                                                           |                                                                                                                                                 |                                                                                                    |                                                              |                                                                 |                     |                    |

| [6]            | Т                           | Temporary bit, bit copy (BLD)And bit storage (BST)Used in instructions,T The bit will be used as a temporary storage bit to temporarily store the value of a bit in the general-purpose register. For details, please refer to the instruction description section |                                                                                                                                                 |                                                                                                    |                                                              |                                                                 |                     |                    |

| [7]            | I                           | interrupt source<br>the interrupt sig<br>interrupt vector                                                                                                                                                                                                          | es are controlled b<br>mal to enter the co                                                                                                      | it must be set to 1 I y independent con ore.I The bit is auto t return instruction I Command chang | trol bits. The glob<br>matically cleared<br>(RETI)Set automa | al interrupt enable<br>by the hardware a<br>tically afterwards. | bit is the back bar | rier that controls |

## General working register

General working register according to LGT8XM Instruction set architecture optimization. In order to achieve the required efficiency and flexibility of kernel execution,

${\tt LGT8XMThe\ internal\ general\ working\ register\ supports\ the\ following\ access\ modes:}$

- Z One 8 Read one bit at the same time 8 Bit write operation

- ${\sf Z}$  two 8 Read one bit at the same time 8 Bit write operation

- Z two 8 Read one bit at the same time 16 Bit write operation

- Z 16 Read one bit at the same time 16 Bit write

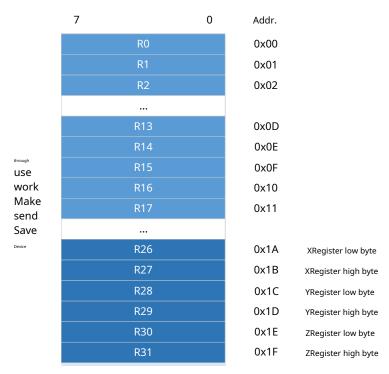

LGT8XM General working register

Most instructions can directly access all general-purpose working registers, and most of them are single-cycle instructions. As shown in the figure above, each register corresponds to an address in the data storage space, and these general working registers are mapped to the data storage space. As soon as they don't really exist inSRAMHowever, this unified mapping storage organization brings great flexibility to access them.X/Y/Z

The register can be used as a pointer to index to any general-purpose register.

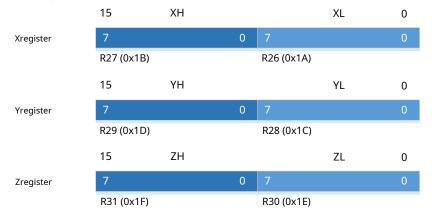

## X/Y/Z register

register R26...R31 Can be combined in two to form three 16 Bit register. These three16 Bit registers are mainly used for indirect Address pointer for addressing access,X/Y/Z The register structure is as follows:

In different addressing modes, These registers are used as fixed offset, auto-increment and auto-decrement address pointers, For details, please refer to the instruction description section.

#### Stack pointer

The stack is used to store temporary data, local variables, and the return address of interrupts and subroutine calls. It is important to note that the stack is not designed to grow from a high address to a low address. Stack pointer register (SP)Always point to the top of the stack. The stack pointer points to the data SRAMThe physical space where it is located, where the stack space necessary for subroutines or interrupt calls is stored. PUSH The instruction will decrement the stack pointer.

Stack in SRAMThe position in must be correctly set by software before subroutine execution or interrupt enable. Under normal circumstances, the stack pointer is initialized to point to SRAMHigh address. The stack pointer must be set to high SRAMStart address. SRAMFor the address mapped in the system data storage, please refer to the system data storage section.

#### Stack pointer related instructions

| instruction | Stack pointer | description                                                                     |  |

|-------------|---------------|---------------------------------------------------------------------------------|--|

| PUSH        | increase 1    | Data is pushed onto the stack                                                   |  |

| CALL        |               |                                                                                 |  |

| ICALL       | increase 2    | The return address of the interrupt or subroutine call is pushed onto the stack |  |

| RCALL       |               |                                                                                 |  |

| POP         | cut back 1    | Data is taken from the stack                                                    |  |

| RET         |               |                                                                                 |  |

| RETI        | cut back 2    | The return address of the interrupt or subroutine call is taken from the stack  |  |

The stack pointer is allocated by I/O Two of space 8 Bit register structure. The actual length of the stack pointer is related to the system implementation. in LGT8XMIn some chip implementations of the architecture, the data space is so small that only SPL Can meet the addressing needs, in this case, SPH The register will not appear.

#### SPH/SPL Stack pointer register definition

|                | SPH/SPL Stack pointer register |          |                  |  |  |  |

|----------------|--------------------------------|----------|------------------|--|--|--|

| SPH: 0x3E      | (0x5E)                         |          | Defaults: RAMEND |  |  |  |

| SPL: 0x3D      | (0x5D)                         |          |                  |  |  |  |

| SP             |                                | SP[15:0] |                  |  |  |  |

| R/W            |                                |          | R/W              |  |  |  |

| Bit definition | Bit definition                 |          |                  |  |  |  |

| [7:0]          | SPL Stack pointer low 8 Bit    |          |                  |  |  |  |

| [15:8]         | SPH Stack pointer high 8 Bit   |          |                  |  |  |  |

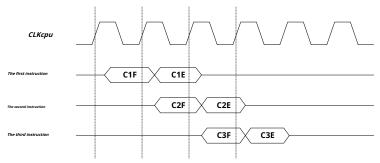

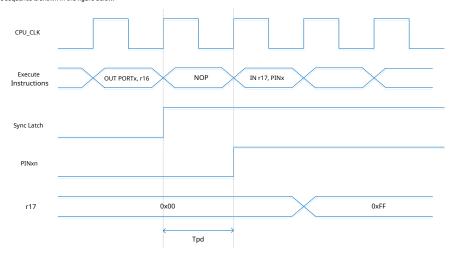

#### Instruction execution timing

This chapter describes the general timing concepts of instruction execution.LGT8XMThe core is clocked by the core (CLKcpu)Drive, this clock comes directly from the clock source selection circuit of the system.

The following figure shows the execution sequence of the instruction pipeline based on the Haval architecture and the concept of fast access to the register file. This is to make

Get the kernel to get 1MIPS/MHz The physical guarantee of the efficiency of the implementation.

As can be seen from the figure above, the second instruction will be read during the execution of the first instruction. When the second instruction enters the execution

During the run, the third instruction will be read at the same time. In this way, during the entire execution period, there is no need to spend extra cycles for fetching instructions.

From the perspective of the pipeline, the efficiency of executing one instruction every Monday is realized.

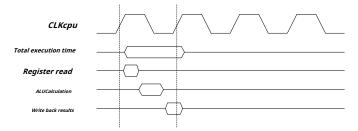

The following figure shows the access timing of the general working register. In one cycle,ALU The operation uses two registers as operands, and in this cycle ALU The execution result is written into the target register.

#### Reset and interrupt handling

LGT8XM Support multiple interrupt sources. These interrupt and reset vectors correspond to an independent program vector entry in the program space. Generally speaking, all interrupts are controlled by separate control bits. When the control bit is set and the global interrupt enable bit of the core is enabled, the core can respond to this interrupt.

The low program space is reserved as the reset and interrupt vector area by default.LGT8FX8P For a complete list of interrupts supported, please refer to the introduction in the interrupt chapter. This list also determines the priority of different interrupts. The lower the vector address of the interrupt, the higher the corresponding interrupt priority. Reset (RESET)Has a high priority, and then INTO – External interrupt request 0.

The start address of the interrupt vector table (except the reset vector) can be redefined to any 256 At the beginning of byte alignment, you need to pass MCU Control register (MCUCR)middle IVSEL Bit and IVBASE Vector base address register implementation.

When the kernel responds to the interrupt, the global interrupt enable flag is I Will be automatically cleared by hardware. Users can passI Bit enable realizes interrupt nesting. In this way, any subsequent interrupts will interrupt the current interrupt service routine. I Bit in the execution of the interrupt return instruction (RETI). It is automatically set afterwards, so that it can respond normally to subsequent interrupts.

There is a basic type of interrupt. The first type is triggered by an event, and the interrupt flag bit is set after an interrupt event occurs. For this kind of interrupt, after the kernel responds to the interrupt request, the currentPC The value is directly replaced with the actual interrupt vector address, the corresponding interrupt service subroutine is executed, and the hardware automatically clears the interrupt flag bit. The interrupt flag bit can also be written to the position of the interrupt flag bit 1 Clear. If the interrupt enable bit is cleared when an interrupt occurs, the interrupt flag bit will still be set to record the interrupt event. After the interrupt is enabled, the recorded interrupt event will be immediately responded. Similarly, if an interrupt occurs, the global interrupt enable bit (SERG.I)Is cleared, the corresponding interrupt flag bit will also be set to record the interrupt event, etc.

After the global interrupt enable bit is set, these recorded interrupts will be executed in order according to their priority.

The second type of interrupt is that when the interrupt condition always exists, the interrupt will always respond. This type of interrupt does not require an interrupt flag bit. If the interrupt condition disappears before the interrupt is enabled, the interrupt will not be responded.

when LGT8XMAfter the kernel exits from the interrupt service subroutine, the execution flow will return to the main program. After executing one or several instructions in the main program, it can respond to other waiting interrupt requests.

It should be noted that the system status register (SREG)It will not be automatically saved after entering the interrupt service, nor will it be automatically restored after returning from the interrupt service. It must be handled by the software.

When using CLI After the instruction disables the interrupt, the interrupt will be immediately disabled. in CLI All interrupts that occur after the instruction will not be responded. Even with CLI The interrupts that occur at the same time when the instruction is executed will not be responded. The following example shows how to use CLI Avoid interruption EEPROM Write timing:

#### Interrupt response time

LGT8XM The kernel is optimized for interrupt response, so that any interrupt 4 A response must be received within one system clock cycle. A fter a system clock cycle, the interrupt service subroutine enters the execution cycle. At this 4 Within clocks, before the interrupt

PC The value is pushed onto the stack, and the system execution flow jumps to the interrupt service routine corresponding to the interrupt vector. If the interrupt occurs during the execution of a multi-cycle instruction, the kernel will ensure that the current instruction ends correctly. If the interrupt occurs while the system is sleeping (SLEEP), The interrupt response needs to be added 4 Clock cycles. This increased clock period is used to synchronize the period of wake-up operation from the selected sleep mode. For a detailed description of the sleep mode, please refer to the relevant chapters on power management.

Need to return from the interrupt service subroutine 2 Clock cycles. At this 2 Within clock cycles, PC Recover from the stack, stack pointer plus 2, And automatically enable the global interrupt control bit.

#### Storage unit

#### Overview

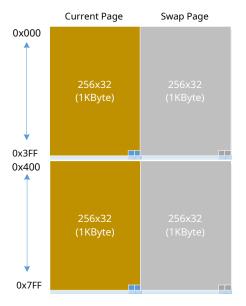

This chapter mainly describes LGT8FX8P Different storage units within the series.LGT8XMThe framework supports two main internal storage spaces, namely data storage space and program storage space.LGT8FX8P Also contains data FLASH, Can be achieved through the internal controller EEPROMData storage function of the interface. In addition,LGT8FX8P The system also contains a special storage unit for storing system configuration information and the chip's global device number (GUID).

LGT8FX8P Series chips include LGT8F88P/168P/328P Four different models; the peripherals and packages of the four models are fully compatible, the difference is FLASH Program storage space and internal data SRAM, The following table is more clear Described LGT8FX8P Different storage space configurations of series chips:

| DEVICE    | FLASH          | SRAM | E2PROM                | Interrupt vector   |                                     |  |

|-----------|----------------|------|-----------------------|--------------------|-------------------------------------|--|

| LGT8F88P  | 8KB            | 1KB  | 2KB                   | 1 Instruction word |                                     |  |

| LGT8F168P | 16KB           | 1KB  | 4KB                   | 2 Instruction word |                                     |  |

| LCTOFOOD  | LCTOF220D 22VD |      | 22VD 2VD              | 2VD                | Can be configured as 0K/1K/2K/4K/8K |  |

| LGT8F328P | 32KB           | 2KB  | (versus FLASH shared) | 2 Instruction word |                                     |  |

LGT8F328P There is no independent internal use for simulation E2PROMInterface FLASH Space; for simulation E2PROMSave

Storage space and program FLASH Sharing, users can choose the appropriate configuration according to application requirements.

Due to simulation E2PROMUnique implementation of the interface, the system requires twice as many programs FLASH Space simulation E2PROM

Storage space, for example for LGT8F328P, If the user configures 1KB of E2PROM

Space, there will be 2KB byte

The program space is reserved, leaving 30KB of FLASH Space is used to store programs.

${\tt LGT8F328P\ program\ FLASH\ versus\ E2PROMS hared\ configuration\ table:}$

| DEVICE    | FLASH | E2PROM |

|-----------|-------|--------|

|           | 32KB  | 0KB    |

|           | 30KB  | 1KB    |

| LGT8F328P | 28KB  | 2KB    |

|           | 24KB  | 4KB    |

|           | 16KB  | 8KB    |

# System programmable FLASH Program storage unit

LGT8FX8PThe series of microcontrollers include8K/16K/32KByte on-chip online programmableFLASHProgram storage unit.

program FLASH Can guarantee at least 100,000 More than two erasing and writing cycles.LGT8FX8P Internal integration FLASH Interface controller, capable of in-system programming (ISP)And the self-upgrading function of the program. For specific implementation details, please refer to this chapter on FLASH The description of the interface controller part.

Program space can also be passed LPMDirect access to instructions (read), this feature can realize application-related constant search

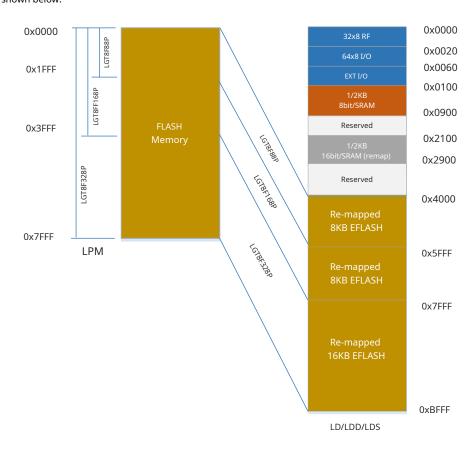

table. SimultaneouslyFLASH The program space is also mapped to the system data storage space, and the user can also use it LD/LDD/LDS Realize right FLASH Space access. Program space is mapped to data storage space0x4000 Within the starting address range.

As shown below:

## SRAMData storage unit

LGT8FX8P A series of microcontrollers is a relatively complex microcontroller, it supports a variety of different types of peripherals, the controllers of these peripherals are allocated in 64 A I/O In the register space. Can pass directlyIN/OUT Command access. The control registers of other peripherals are allocated in0x60 ~ 0xFF In the area, since this part of the space is mapped to the data storage space, it can only be passed through ST/STS/STD as well as LD/LDS/LDD Wait for instruction to visit.

LGT8FX8P System data storage space from 0 Starting from the address, the general working register files are mapped respectively,I/O Space, expansion I/O Space and internal data SRAM space. The beginning32 Byte address correspondence LGT8XM Kernel 32

A general-purpose working register. Next64 Addresses can be passed IN/OUT Direct access standard for instructions I/O space. Then160 Addresses are extensions I/O Space, the next step is more 2K Bytes of data SRAM. From0x4000 Start to 0xBFFF This part of the ending space is mapped FLASH Program storage unit.

In the system 1K/2K byte SRAM Are mapped to two spaces respectively. From0x0100 Start to 0x0900 This space ended by the kernel with 8 The width of the bit byte is read and written. From0x2100 Start to 0x2900 End this area as 16 Bit-width access space. systemRAMIs mapped to 0x2100 The first high address is mainly used to cooperate uDSU Module work to achieve efficient 16 Bit data storage. When programming, the ordinary8 Bit addressing variable address plus 0x2000, You can switch to 16 Bit access mode.

System Support 5 Different addressing modes can cover the entire data space: direct access, indirect access with offset, indirect access, indirect access with decrement address before access, and indirect access with increment address after access. General working register R26 To R31 Address pointer used for indirect access. Indirect access can address the entire data storage space. Indirect access with offset address can be addressed toY/Z Register is near the base address 63 Address spaces.

When using the indirect register access mode that supports address auto-increment/decrement, the address register X/Y/Z It will be automatically decremented/incremented by the hardware before/after the access occurs. For details, please refer to the instruction set description section.

16 Bit register X/Y/Z And the related automatic addressing mode (increment, decrement), in 16 The bit extension mode also plays a very important role.16 Bit extension mode can be used LD/ST Increment/decrement mode for realizing automatic increment and decrement addressing with variables. This mode is very effective when performing operations on arrays. For specific implementation, please refer to Digital Computing Accelerator (uDSU) Related chapters.

## Universal I/O register

LGT8FX8P of I/O There are three general I/O register GPIOR2/1/0, These three registers can be used IN/OUT Command access, used to store user-defined data.

#### Peripheral register space

I/O For detailed definition of space, please refer to LGT8FX8P Data sheet"Register overview"chapter.

LGT8FX8P All peripherals are assigned to I/O space. allI/O Space address can be LD/LDS/LDDD as well as ST/STS/STD Command access. The data accessed is all through32 A general-purpose working register is passed. in0x00 ~ 0x1F between I/O Registers can be addressed by bit addressing instructions SBI with CBI access. In these registers, the value of a certain bit can be usedSBIS with SBIC Instruction detection is used to control the execution flow of the program. For details, please refer to the instruction set description section.

When using IN/OUT Command access I/O Must be addressed when registering 0x00 ~ 0x3F Between addresses. When usingLD or ST Command access I/O Space, must pass I/O The space in the system data memory is uniformly mapped to the mapped address access of the space (plus 0x20 Offset). Some other allocations are in expansionI/O Peripheral registers of space (0x60 ~ 0xFF), Can only use ST/STS/STD with LD/LDS/LDD Command access.

In order to be compatible with future devices, reserved bits must be written during write operations 0. Can not be reservedI/O Perform a write operation on the space.

Some registers include status flags and need to be written 1 To be cleared. have to be aware of is,CBI with SBI The instructions only support specific bits, so CBI/SBI It can only work on the registers that contain these status flags. In addition, CBI/SBI The instruction can only work on 0x00 To 0x1F Registers in this address range.

## FLASH Controller (E2PCTL)

LGT8FX8P The internal implementation integrates a flexible and reliable EFLASH Read and write controller, can use the existing data in the systemFLASHStorage space, storage space for byte read and write access, similar toE2PROMStorage applications; E2PROM

The interface simulation adopts the algorithm of erasing and writing equalization, which can transfer the data FLASH Increased life cycle 1 About times, can guarantee 100,000 More than two erasing and writing cycles.

E2PCTL The controller also implements FLASH The online erasing and writing operation of the program space can be realized online by the software.

The function of upgrading the firmware automatically. byFLASH Controller access program FLASH Program space, only supports page erase (1024 Bytes) and 32 Bit width read and write access.

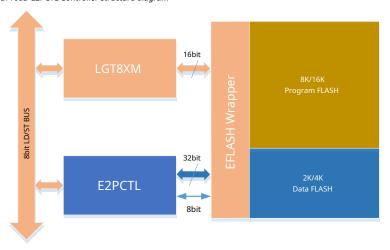

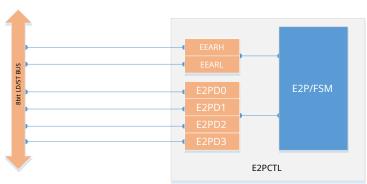

#### LGT8F88D/168D E2PCTL Controller structure diagram

E2PCTL simulation E2PROM Function access data FLASH Space, can support 8 Bit, 32 Bit read and write width. visit

Ask the program FLASH Space, support page erasing and 32 Bit data read and write. due toLGT8FX8P internal FLASH The small storage unit is 32

Bit, so it is recommended to use 32 Bit access mode, especially for write operations. 32 Bit-accessed read and write operations are not only

efficient, but also conducive to protection FLASH The erasable life of the storage unit.

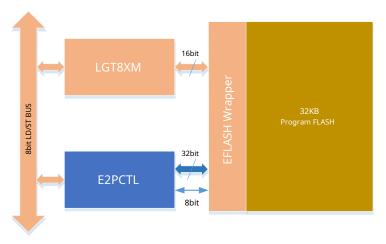

LGT8F328P E2PCTL Controller structure diagram

LGT8F328P No extra data inside FLASH. therefore,LGT8XM Kernel and E2PCTL Shared internal 32K word Section FLASH storage. Users can change32K byte FLASH The space is divided into program space and data space. By configurationE2PCTL Controller, can be set to simulate E2PROM The size of the space.E2PCTL Use page swap mode to achieve simulation E2PROM Logic, algorithm in page (1K Byte) as the unit. So simulate1K Byte E2PROM Space, need to occupy 2K Byte FLASH Space, and so on, to achieve 4K Byte E2PROM, Need to occupy 8K Byte

FLASH space. For specific implementation methods, please refer to E2PCTL The description of the algorithm implementation.

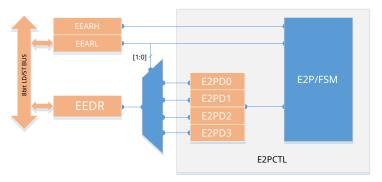

## **E2PCTL Data register**

E2PCTL Inside the controller 4 Bytes of data buffer (E2PD0~3), this 4 Byte buffer composition

Last visit

FLASH Spatial 32 Bit data interface.

when E2PCTL When the controller works in byte read and write mode, EEDR As an interface for reading and writing byte data, E2PCTL more EEARL[1:0]Load the data into the correct data cache based on the current address information FLASH The data of the target address complements the other three bytes of data, and the combination will be complete 32 Bit data updated to FLASH in.

when E2PCTL work at 32 In bit read/write mode, it can still be used at this time EEDR Register as a common data interface, through EEARL[1:0]As an address to address the internal data buffer, a complete read and write 32 Bit data. In addition, you can directly use the data cache to map toIO Direct access to the registers of the space (E0~3).

E2PCTL work at 8 Schematic diagram of data access in bit byte read and write mode:

E2PCTL work at 32 Schematic diagram of data access in bit word read and write mode:

Byte mode is used for backward compatibility LGT8FX8D The byte read and write mode.LGT8FX8P Built-in FLASH for 32 Bit interface width, use 32 Bit read and write mode will give read and write efficiency and FLASH The erasing life brings great benefits, so it is recommended to use 32 Bit read and write mode.

#### E2PCTL simulation E2PROMInterface algorithm

we know, FLASH The memory must be erased before being written, and the erase operation is in units of pages.LGT8FX8P

Built-in FLASH The size of one page of memory is 1K byte. Therefore, in order to update a byte of data in the page, it is also necessary to erase the data of the entire page first, then update the target address data, and restore the data of other bytes in the page at the same time. The entire operation is not only time-consuming, but also brings Risk of accidental data loss due to power supply.

E2PCTL Internal use of page swap algorithm to achieve simulation E2PROM. The page swap algorithm mode can ensure that the original data will not be lost due to unexpected conditions such as power failure when the page erase operation is performed. At the same time exchange algorithm use2 Page space

The exchange method is used alternately, and simulation is also added E2PROMThe service life of the space.

In terms of efficiency, E2PCTL The controller implements a continuous data update mode, which reduces the repeated erasing and writing process caused by repeated data update.

In terms of implementation, E2PCTL Manage each page separately, and after occupying one page 2 Bytes are used as page status information. So users are using greater than 1K of E2PROMWhen simulating the space, you need to pay attention to the address crossing 1K Spatial Special treatment. Because every 1K Spatial Rear 2 Bytes reserved for E2PCTL Use, the user can't 2 Bytes

The space performs normal reading and writing.

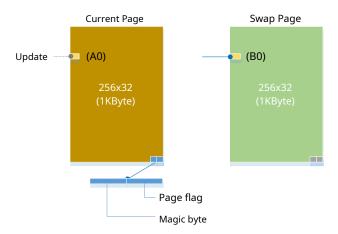

The picture below is E2PCTL Logic diagram based on page swap algorithm:

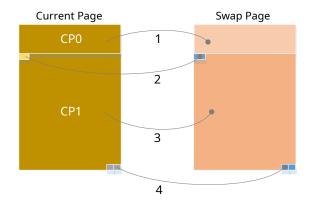

as the picture shows,E2PCTL internal use 2 Each page simulates one page size E2PROM space. These two pages

One is marked as the current page, and the other is an exchange page.E2PCTL After using the page 2 Bytes store page information. When we

need to update a certain byte in the page, such as the picture aboveA0 byte. First, we will not erase the current page, but the swap page. Then

divide the current page into 3 Part of the operation. First is inA0 In the previous data, we call this part of the space CP0,After that A0 After the data,

this part of the space is CP1.E2PCTL According to user configuration, CP0 The corresponding data is copied to the corresponding address of the

exchange page, and then the data that needs to be updated is written to the address corresponding to the exchange page (B0), Followed by copy

CP1 The data to the exchange page.

After completing the above operations, the data has been exchanged, but the page status has not been updated. Therefore, if a power failure or other abnormality occurs before this, because this update operation has not been completed, the previous data will not be destroyed, ensuring the integrity of the data. If everything goes well, E2PCTL Will be at CP1 After the data is exchanged, the updated page status is written to the page information of the previous exchanged page to realize the replacement of the face-to-face page. After that, the exchange page becomes the current page.

E2PCTL The page exchange process is shown in the figure below (1->2->3->4):

When the system is configured E2PROMSimulation space is greater than 1KTime, E2PCTLStill take the page as Small unit realization E2PROM Space simulation algorithm. For example, if the user configures 2K of E2PROMArea, actually E2PCTL Will occupy 4 Pages (4K) Space. among them 2 Pages as a group, used to simulate a page size E2PROM space.

Need to pay attention to the user configuration 2K Byte E2PROM The space is not continuous, because the bytes of each page will be used to store page status information.

Rear 2 A

#### E2PCTL Continuous programming mode

Due to passing E2PCTL Updates will cause page swaps. The swap page will be erased during the page swap process. Page erasing not only takes time, but also increases FLASH Loss of life. thereforeE2PCTL Added continuous write mode. In continuous write mode, users can update continuouslyE2PROM Area, the page swap operation will only be performed after consecutive addresses. For applications that need to continuously update a whole block of data, the continuous mode is more effective.

Continuous programming mode E2PCTL Control register ECCR of SWM Bit enable. After the continuous mode is enabled, subsequent write operations will directly write the data to the address corresponding to the swap page. SWMIn mode, the write operation will not be executed CP0/1 Area data copy operation. Before writing the last byte, the software passes SWMD is able continuous mode, then execute write, after that E2PCTL

Will execute the complete CP0/1 Copy operation and update page status information.

#### **E2PCTL Read and write FLASH Program space**

by E2PCTL Controller, can realize the program FLASH Read and write access to the space. And simulationE2PROM The difference is that through E2PCTL On the program FLASH Access to the space requires software control. Proceed as follows:

- 1. To erase the target page, the target page needs to be erased before updating the data, and the page address is passed EEAR The register is given.

CorrectFLASH For page erasing command control, please refer to EECR The definition of the register;

- 2. programming FLASH Space must be 32 Bits are small units. byE2PD0~3 Set data;

- ${\it 3. The destination address is determined by EEAR Register given, address EEAR [1:0] Will be ignored}\\$

by E2PCTL Read and write program FLASH Space, can realize online program update (IAP)The function is very useful in some applications that need to update application data on site and provide customized product updates.

#### **E2PCTL Interface operation process**

E2PCTLThe controller is working mainly through4Implementation of a register, respectivelyE2PCTLControl status registerEECR, ECCR; Data register EEDR(E2PD0~E2PD3)And address register EEAR(EEARL/EEARH).

ECCR Register is used to set E2PCTL Working status, most of the status needs to be in E2PCTL The setup is completed before work, and this process is generally implemented during system initialization. ECCR In the register SWM This bit is used to enable continuous write mode. This control bit needs to be set during continuous write operation.

EECR The register is used to control the selection operation type, and is used to select operation instructions, such as setting read and erase commands.

EEDR Register is used 8 Bit byte mode interface,E2PD0~3 Used for 32 Bit pattern read and write operations;

EEAR The register is used to set the target address of reading and writing, and also used to set the page address of the page erase operation. Page address is Aligned in page units, the size of a page is 1K Bytes, need attention EEAR The specified address is a byte address.

## by E2PCTL Interface access FLASH Program space:

by E2PCTL The interface can be implemented FLASH Reading and writing and erasing of program space. CorrectFLASH Reading and writing of space only supports

hod Bit access width. The erase operation is in page units, the size of each page1K byte(256x32). WritingFLASH Before the program space, first erase the page where the target address is located. E2PCTL write FLASH Program space

Continuous mode is not supported, users need to complete write operations in sequence. The following is erasedFLASH The flow of the program space:

#### 1. program FLASH Page erase operation

- Z Set up EEAR[14:0]For the target page address that needs to be erased, the program FLASH One page size is 1K Bytes, therefore EEAR[14:10]Will be used as the page address, EEAR[9:0]Set as 0

- Z Set up EEPM[3:0] = 1X01,among them EEPM[2]Can be set to 0 or 1

- Z Set up EEMPE = 1, Simultaneously EEPE = 0

- Z In four cycles, set EEPE = 1,starting program FLASH Wipe process

#### 2. program FLASH Programming operation

- Z write E2PD0~3,ready 32 Bit programming data setting EEAR Is the target

- Z address, where the address is 4 Byte alignment setting EEPM[3:0] = 1X10,

- Z among them EEPM[2]Can be set to 0 or 1

- Z Set up EEMPE = 1,Simultaneously EEPE = 0

- Z In four cycles, set EEPE = 1,start up FLASH Programming process

#### by E2PCTL Interface access E2PROMSimulation space:

E2PCTL Controller through simulation E2PROM Interface logic to access data FLASH space. simulationE2PROM stand by 8

Bit,16 Bit and 32 Read and write access to bit data width.8 Bit byte pattern pair E2PROMThe interface has better compatibility.

32 Bit mode helps to improve storage efficiency and FLASH Life, therefore 32 The bit read and write mode is the recommended read and write mode.E2PROMThe analog interface supports continuous read and write mode. It has obvious advantages in data applications that need to update multiple continuous addresses at a time and is recommended.

for LGT8F88P/168P,data FLASH For independent storage space. No need to passECCR Register configuration and use

CaffLASH Data space.LGT8F328P There is no independent data FLASH Space, data FLASH And program FLASH Total

enjoy 32K byte FLASH space. Need to passECCR Register enable data FLASH Partition function and pass ECCR Deposit

Mechanical ECS[1:0]Bit configuration data FLASHthe size of.

After the configuration takes eff@ther methods of use and LGT8F88P/168P the same.

FLASH The controller is implementing E2PROMWhen the interface is used, the internal data has been automatically erased when necessary FLASH Logic, so EPROMThe erase command is optional. This command is only used when the user needs to perform the erase alone.

EECR Register control FLASH Erasing/writing timing, including program FLASH with E2PROM. The specific operation type needs to pass EECR Register EEPME with EEPM[3:0]set up. CorrectE2PROMThe read operation is relatively simple, after setting the target address and mode, write EERE Corresponding to the target address 32 Bit data read in FLASH Inside the controller, the user can pass EEDR The register reads the byte of interest.FLASH The controller does not implement the program FLASH Space read operation, users can use it conveniently LPM Or through the program FLASH Used at the address of the data unified mapping space LD/LDD/LDS The instruction is read.

#### 1. 8 Bit pattern, programming E2PROM

- Z Set the target address to EEARH/L register

- z Set new data to EEDR register

- Z Set up EEPM[3:1] = 000,EEPM[0]Can be set to 0 or 1

- Z Set up EEMPE = 1, Simultaneously EEPE = 0

- z In four cycles, set EEPE = 1

When the setting is complete, FLASH The controller will start the programming operation, during programming CPU It will remain at the current instruction address and will not continue to run until the operation is completed. During the programming process, if you need to erase dataFLASH, FLASH The controller will automatically start the erasing process.

#### 2. 32 Bit pattern, programming E2PROM

- Z by E2PD0~3,ready 32 Bit data sets the target address to EEARH/L register. Note that this is a byte-

- Z aligned address,FLASH For controller EEAR[15:2]As a visit FLASH the address of. Set upEEPM[3:1] = 010,EEPM[0]Can be set to 0 or 1

- Z Set up EEMPE = 1, Simultaneously EEPE = 0

- z In four cycles, set EEPE = 1

## 3. 8 Bit pattern, read E2PROM

Z

- Z Set the target address to EEARH/L register

- z Set up EEPM[3:1] = 000

- Z Set up EERE = 1 start up E2PROMRead operation waiting 2 Cycles

- Z (execute two NOP Operation) The data corresponding to the target

- Z address is updated to EEDR register

#### 4. 32 Bit pattern, read E2PROM

- Z Set up EEARH/L Is the target address, the address is 4 Byte

- Z alignment setting EEPM[3:1] = 010, Turn on 32 Bit interface mode

- Z setting EERE = 1,start up E2PROMRead operation waiting 2 System

- Z clock cycles (execute two NOP instruction)

E2PCTL Access simulation E2PROMSpace, support continuous programming mode, continuous access mode is very efficient for applications that need to update one data block at a time, and also help to improve FLASH Service life. Continuous programming mode only supports32 Data programming operation of bit width.

Continuous access mode passed ECCR Register SWMBit enable.SWMAfter enabling, the next pass E2PCTL Write simulation E2PROMSpace operations are in continuous programming mode. In continuous programming mode, E2PCTL The controller will automatically process the page change according to the data situation in the target address. However, if a page change occurs during the continuous programming mode, the controller will not automatically change the CPO/1 The data exchange of the area will not update the page information.

When continuous programming to the next operation, clear through SWMBit to turn off the continuous programming mode, and then in the non-SWMA programming operation after starting in the mode, after the programming is over,E2PCTL Will automatically CP0/1 The data of the area is copied to the swap page, and the information of the swap page is updated to make it the current valid page, thereby completing the entire continuous programming operation.

#### 5. Continuous programming mode operation process:

- 1. by ECCR Configuration Data FLASH Size and enable SWMBit

- 2. use 32 Bit mode programming simulation E2PROMarea

- 3. If it is not the next operation, go back to step 2 Continue to program the next data

- 4. If it reaches the next programming, first pass SWMDisable continuous programming mode, then use steps 2 Programming once after the completion of the operation flow

#### **E2PCTL Efficient FLASH Data management**

E2PCTL In addition to the continuous programming mode, the controller can also pass ECCR Register CP0/1 Bits carry out independent control of data exchange and copying during the page swapping process. ECCR Register CP0/1 Respectively used to control the page exchange process for the current page CP0/1 Exchange operation of area data. Cleared CP0/1 Bit, the data of the corresponding area in the current page will not be exchanged during the page exchange process. An efficient management method provided in this section will take advantage of this feature.

in FLASH During the data update process, a time-consuming operation occurs during the swap page erasing process. Therefore, we can address a data management method that greatly reduces the number of page erases, which can improve programming efficiency and reduce life loss.

Here we provide a reference algorithm for data management applications based on data blocks:

- 1. Assuming that user data is just a complete data block, the size of the data block 4 Integer multiples of bytes;

- 2. Each data update will update a complete data block

- ${\it 3.}\ In\ addition\ to\ storing\ user\ data,\ data\ block\ information\ also\ needs\ to\ store\ a\ block\ management\ information$

Under the above three conditions, we can make full use of E2PCTL Continuous programming mode and automatic page switching mechanism to achieve An efficient FLASH Data management methods.

Since the data updated each time is a data block of the same size, and the address information pointing to the next block of data is stored in the data structure of each block, we can program in the order of the address each time the data is updated FLASH, No need to do CP0/1 Data replication. At the same time, since the data is updated to an erased area each time, page erasure will not occur.

When the data is written, the next data area pointed to by its structure information returns to the starting address of the page. After that, data write operations occur again, EZPCTL A page erasing process will be initiated and the current active page will be updated.

#### FLASH Operational protection measures

in case VCC The voltage is low, FLASH Erase and write operations may cause errors due to low voltage.

FLASH/There may be two reasons for the error of data erasing and writing operation under low pressure. First of all, normalFLASH Erase and write operations require a small operating voltage. Below this voltage, the operation will fail and cause data errors. The second reason is that the core is running at a certain frequency and also requires a small voltage requirement. When the voltage is lower than this voltage, it will cause an error in the execution of instructions, which willFLASH An error occurred in the operation.

You can avoid similar problems in the following simple ways:

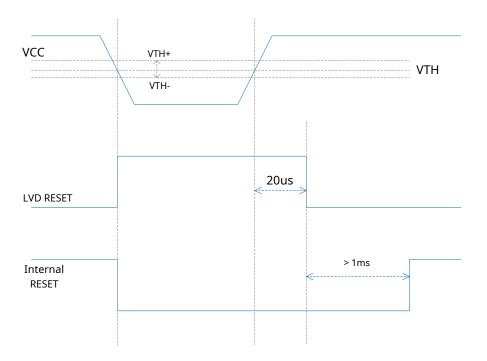

When the supply voltage is low, let the system enter the reset state. This can be achieved by configuring the internal low-voltage detection circuit (VDT) achieve. in caseVDT It is detected that the current working voltage is lower than the set threshold, VDT A reset signal will be output. in case VDT The threshold value of can not meet the needs of the application, you can consider adding a reset circuit externally.

#### Register description

## FLASH Address register- EEARH/EEARL

|                    | EEARH/EEARL                                  |  |                  |  |  |  |

|--------------------|----------------------------------------------|--|------------------|--|--|--|

| EEARH: 0x22 (0x42) |                                              |  | Defaults: 0x0000 |  |  |  |

| EEARL: 0x21 (0x41) |                                              |  |                  |  |  |  |

| bits               | EEAR[15:0]                                   |  |                  |  |  |  |

| R/W                | R/W                                          |  |                  |  |  |  |

| Bit definition     | Bit definition                               |  |                  |  |  |  |

| [7:0]              | EEARL EFLASH/E2PROMLow access address 8 Bit. |  |                  |  |  |  |

| [14:8]             | EEARH EFLASH/E2PROMHigh access address 7 Bit |  |                  |  |  |  |

| [15]               | - reserved                                   |  |                  |  |  |  |

When using E2PCTL Controller access program FLASH Area, EEAR[14:2]For access to 4 Byte aligned integer A program space. EEAR[1:0]Only accessing data registers EEDR When used. For details, please refer to the following about EEDR The description of the data register. E2PCTL Controller support 8/16/32 Bit mode, no matter which mode, here EEAR All addressing is byte-aligned.

## FLASH Data register- EEDR/E2PD0

|                           | EEDR/E2PD0 – FLASH/E2PROMData register 0 |                              |                          |  |  |

|---------------------------|------------------------------------------|------------------------------|--------------------------|--|--|