Fórum témák

» Több friss téma |

Cikkek » Egyperces: Logikai szintillesztések (#3) Egyperces: Logikai szintillesztések (#3)

Szerző: Topi, idő: Máj 1, 2020, Olvasva: 17151, Oldal olvasási idő: kb. 6 perc

Rövid áttekintés néhány, sűrűn használt szintillesztő megoldásról

A sorozat többi része:

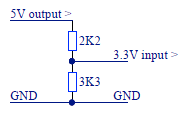

Van pár szintillesztő megoldás, amivel nap mint nap találkozhatunk. A logikai szintillesztés egyik legfontosabb kulcsának én azt tartom, hogy a célra válasszunk szintillesztő megoldást, és ne mindig a megszokás vezérelje a tervezőt. Célhoz kötöttségAzért fontos a kívánt célhoz választani illesztő megoldást, hogy olcsóbb és egyszerűbb legyen. Vizsgálandó elvek: - Kell-e push-pull (vagy totem-pole*) kimenet, vagy egy open-collector (open-drain) vonalat kell illeszteni - Milyen órajel / frekvencia a megkívánt, pár Hz, pár száz KHz vagy megahertz-ek - Kimeneti impedancia amire szükség van - Kell-e kétirányú illesztés. A kétirányúság automatikus-e, vagy vezérelt * totem-pole: a totem-pole nem egyenértékű a push-pull megoldással. A totem-pole megoldás régebben sűrűn használt megoldás volt, ugyanis a totem-pole kialakítás két NPN tranzisztorból épül fel, míg a push-pull az egy PNP-NPN párosból. Azért csak régen volt jelentősége, mert amíg a félvezető gyártás gyerekcipőben járt, addig sokkal egyszerűbb volt NPN struktúrát létrehozni, mint PNP-t (ezért is volt drágább a PNP tranzisztor). Mára már ez a határ elmosódott / eltűnt, olcsóbb és egyszerűbb PNP-NPN párost alkalmazni, mint a totem-pole hajtáshoz plusz tranzisztorokat, vagy plusz PN átmenetet (diódát) használni. Főleg úgy nincs mára már totem-pole, mert szinte minden hasonló célú kimenet push-pull MOSFET-ből áll, sokszor közös hordozón, közös SiO2 dielektrikummal "egy alkatrészként" összegyógyítva, majd CMOS komplementer kimenetnek elnevezve. KétirányúságAz automatikus kétirányú megoldásoknál nincs irányt meghatározó bemenet, DIR pin, vagy hasonló. Felépítéséből eredően automatikusan "veszi észre", hogy melyik a kényszerítő-meghajtó oldal, és melyik a bemeneti oldal. A nem automatikus megoldások esetén van irányt meghatározó DIR pin. Ezen megoldások rendszerint nagyobb átviteli sebességet tesznek lehetővé, jóval nagyobb jelmeredekséggel (slew-rate), hiszen belül minden logikai jelszint domináns jelszint (direkt meghajtott), nincs recesszív állapot (ellenállással "mozgatott"). Domináns-recesszív állapot, hasonlóan, mint a CAN-busznál (a CAN-buszról majd értekezünk még egy másik Egyperces részben). Input-output jelek az alábbi rajzokonA könnyen érthetőség kedvéért nyilakkal jelöltem az áramirányokat. 5V output olyan kimenetet jelent, mely 5V-os jelszintet ad. Ilyen például egy 5V-os mikrovezérlő. A 3.3V input olyan bemenetre kötendő, mely 3.3V-os logikai jelszinttel dolgozik. A jelölés tehát az a kimenetfajta, ahonnan a jel származik. A nyíl pedig a jel irányát jelenti, hogy honnan-hova konvertálás történik. Az egyirányú feszültségosztóA feszültség osztó a legegyszerűbb egyirányú szintillesztő.

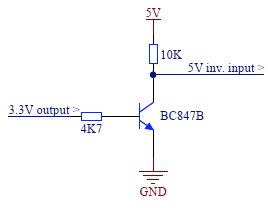

Az osztás értelem szerűen csak magasabb feszültségszintről alacsonyabb feszültség szint felé egyirányban működik. Osztó számolása Ohm-törvénye, feszültségosztó szerint. Egyszerű open-drain vagy open-collector invertáló szintillesztésEzt mindenki ismeri, így hajtunk reléket, nagyfogyasztókat, stb.

Nyugalmi helyzetben (0V a bal oldalon, a 3.3V kimeneti szintet produkáló eszköztől) a jobb oldalon kimeneten az 5V logikai szintet váró ponton 5V jelszintet ad. A bal oldalon 3.3V-os kimenet aktív (3.3V kimenet) esetén pedig, a jobb oldali 5V-os oldalon 0V jelszint jelentkezik. Kimenete open-collector jellegű. Egyszerű open-drain, vagy open-collector nem-invertáló szintillesztésEz már általánosságban kevésbé használt, mert "bonyolult".

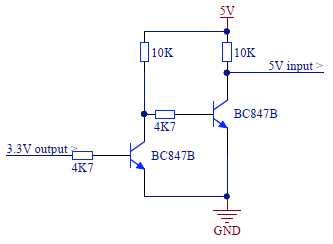

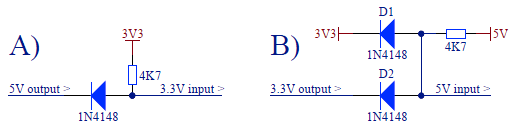

Itt már nem negált a kimenet. Amennyiben a 3.3V-os logikai igaz szintet adó mikrovezérlő kimeneti lába aktív, úgy az áramkör jobb oldala is 5V-os logikai igaz szintet ad ki. Kimenete open-collector jellegű. Egy irányú diódás szintillesztőA diódás szintillesztés egyszerű egyirányú illesztés. Megépíthető oda-vissza konvertálási céllal is, ám ebben az esetben a két irány kialakítása eltérő.

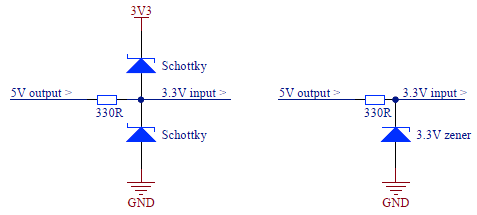

Az "A" megoldás 5V-os logikai jelszintet szolgáltató kimenetet illeszt 3.3V-os bemeneti jelszintet váró eszközhöz. Ha a bal oldal 5V, akkor a jobb oldal 3.3V, ha a bal oldal 0V akkor a kimenet 0.6V (dióda nyitófeszültség távolság). A "B" megoldás (ősrégi Microchip DS41285A application note megoldása, 2008) pedig 3.3V-os logikai jelszintet adó kimenetet illeszt 5V-os bemenetre. Ha a bal oldalra csatlakozó 3.3V-os kimenetet adó eszköz 3.3V-ot ad, akkor a 4K7-el felhúzott 3.9V-ot (3.3V+0.6V) ami már 5V-os logikai szintek esetén igaz (5V CMOS már 3.5V felett logikai igaz), míg a bal oldalon 0V a kimeneten 0.6V-ot ad (5V CMOS már 1.5V alatt logikai hamis). Kimenete open-collector jellegű. Szerzői jótanács: Egyik diódásat se használd. XXI. század van, sok jobb megoldás van már, ami nem határra tervez. Impedancia-szabályzott szintillesztő, Zener szintillesztőAz impedancia-szabályzott szintillesztő azt használja ki, hogy vagy az IO-ba épített védődiódák, vagy a külön kialakított védődiódák megfogják a bemeneti feszültséget például 3.3V és 0V között. Azért tudják megfogni, mert az odavezetés impedanciája annyira nagy, hogy az 5V-os érkező jelszint nem tudja felhúzni a dióda miatt a lábat.

A két schottky dióda megvédi a 3.3V-os bemeneti oldalt, hogy az 5V-os kimenet ne tudja felhúzni. Az alsó schottky dióda igazából elhagyható, viszont szándékkal rajzoltam be, ugyanis így sokaknak ismerős lehet ez a dióda elrendezés, mikrovezérlők IO-jának védődiódájaként. Azok ugyanis használhatók szintillesztési célra is, ha megfelelően alacsony szinten tartjuk a befolyó áramot. Magas befolyó áram egyrészt a diódát károsítja, másrészt pedig felhúzza magát a 3.3V-os tápfeszültséget is. A soros ellenállás az áramkorlátozó szerepet látja el. Jelen példában a 330R azt jelenti, hogy I = U/R = (5V-3.3V)/330R = 5.1mA maximum áramot enged be. Azaz maximum 5mA terheli a felső védődiódát. Adott esetben ez az érték nagy lehet, így 1K is bátran alkalmazható, ha kellően alacsony az adatátviteli sebesség, és nagyon alacsony a 3.3V-os bemeneti oldal kapacitása. A 330R-nak akkor van jelentősége, amikor a Zéner diódás második megoldást alkalmazzuk, ugyanis a névleges letörési feszültséget 5mA ellenirányú előfeszítés mellett éri el a Zener dióda. A 3.3V fölötti feszültséget megfogja a Zener dióda a különbség pedig a Zener dióda és ellenállás pároson hővé alakul. I2C, vagy TWI* egyszerű szintillesztéseAz I2C-t (I2C) relatíve könnyű szintilleszteni, mert open-drain kimenet felépítésű buszról van szó, így az illesztésnél az egyetlen közös potenciáljuk a GND, így csak a GND-re húzást kell megvalósítani. Viszont az egyik vonalnak (SDA, adatvonal) automatikusan kétirányúnak kell lennie. Az SCL órajel lábnál ha csak nem multi-master, akkor csak a master oldalról kell inputnak lennie, slave irányba open-drain is lehet és push-pull is lehet, de a protokoll open-draint ír elő.

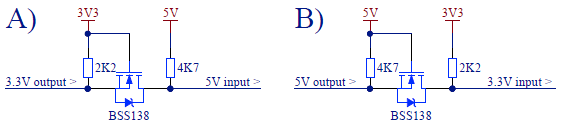

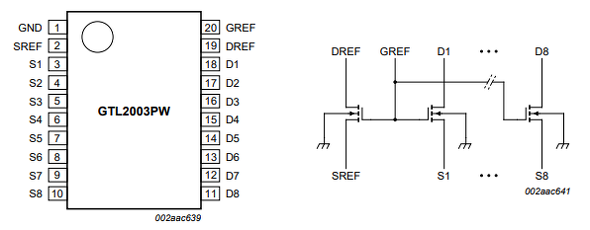

A működése egyszerű, sok Arduino kedvelő találkozhatott vele, mert ott szeretik használni az Arduino 5V-os jelszintje és a szinte minden más 3.3V-os jelszintje miatt. Sokszor a használó nem is tudja, mert a távolkeleti kollégák rácsempészik már alapból a kínai modulokra, hogy az IC-kből ne jöjjön ki azt azokat működtető füst a nem megfelelő 5V-os jelszint miatt. Az "A" megoldás esetén a low-side (3.3V) vezérelt, és 5V oldal (high-side) a bemenet. A "B" megoldás ennek fordítottja. Viszont mindkét megoldás alkalmazható oda-vissza illesztésre. A felhúzó ellenállások értékei azért különböznek, mert az I2C szabvány meghatározza a felhúzó ellenállás értékét. Négy irányt veszünk górcső alá az "A" rajz alapján: - Low-side a vezérelt, alacsony jelszintű 0V: A bal oldal alacsony jelszintje esetén a MOSFET source lába 0V-ra kerül, a gate-je 3.3V-on van, így a drain lábát 0V-ra (source-ra) kapcsolja, így a jobb oldal 0V-on lesz. - Low-side a vezérelt, magas jelszintű 3.3V: A bal oldal magas szintje egyezik a MOSFET gate feszültségével, így nem nyit ki a MOSFET, így az 5V-os jobb oldal logikai magas szinte van a 4K7-es felhúzó ellenállásnak köszönhetően. - High-side a vezérelt, alacsony jelszintű 0V: A jobb oldalon 0V a MOSFET védődiódáján keresztül lehúzza a bal oldalt, így ott is 0V (+ védődióda nyitófeszültsége) lesz. - High-side a vezérelt, magas jelszintű 5V: A jobb oldalon 5V nem mozdítja ki az áramkört a nyugalmi állapotból, így a bal oldalon is a felhúzó ellenállás miatt 3.3V marad. Kétirányú működés ezen fentiek vegyes módja, ahol egyik irányban a MOSFET-ben található védődióda lép működésbe, a másik irányban pedig kinyitásra kényszerítjük a MOSFET-et. Kimenete open-drain jellegű. Ennél a megoldásnál oda kell figyelni, hogy a gate-source kapacitás nagyon alacsony értékű legyen, lehetőleg 100pF alatt. Vagy másik irány esetén a gate-drain kapacitás, hiszen ha ezen kapacitások nagy-értékűek (tehát az alkalmazott MOSFET nagyáramú) akkor a jelmeredekségek nagyon rosszak lesznek (alacsony slew-rate), ugyanis meg kell várni míg feltöltődnek a parazita kapacitások a MOSFET-ben. A fizika itt is működik: nagy áramú MOSFET = vastag rétegszerkezet = nagyobb parazita kapacitások = rosszabb jelmeredekség. * TWI: TWI igazándiból a licensz díjat fizetni nem akaró Philips I2C, de gyakorlati szempontból ugyan az, annak ellenére, hogy a TWI-ba belecsempésztek még extra funkciókat és kivették a 10-bites címzést, de véleményem szerint csak azért, hogy a Philips ne nyújtson be szabadalomjog megsértést az Atmel-el szemben, annak meg ne kelljen licensz díjat fizetnie az IP (Intellectual property - szellemi tulajdon) használat miatt minden egyes Atmel AVR-re. Földelt Gate NMOS megoldásokIlyen IC például a GTL2003 is, mely automatikus irányváltást biztosít, totem-pole kimenettel 0.8V-tól 5V-ig, egy tokban sok csatornával. Az IC már NRND (not recommended for new design) címkés az NXP-nél, persze ha valaki ismeri a lábazonos alternatíváját, írja meg nekem

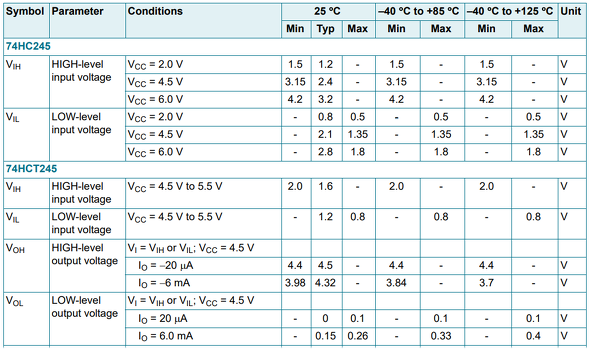

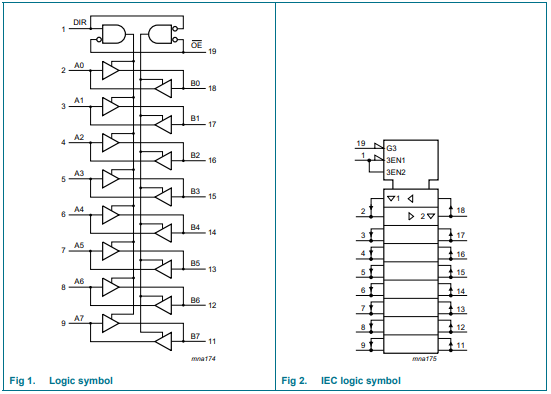

Működését a speciálisan felépített közös gate NMOS-nak köszönheti. Pufferek a 74HC, 74LV családbólEzen megoldás esetén CMOS komplementer kimenetünk lesz, és egyirányú, de adott esetben DIR lábbal ellátva vezérelten kétirányúvá tehető. 74HC245/74HCT245 példa Alapvetően ez egy 8 csatornás 3-state puffer IC, de mivel logikai alacsony és magas jelszint határai illeszkednek a 3.3V-os jelszinthez (bár a sima HC magas jelszintjének minimum értéke már közel van nagyon a 3.3V-hoz, de a tipikus érték 5V-ra 2.9V környékére adódik), mégis alkalmas a feladatra. Kifejezetten erre a célra készített LVCMOS verziója az SN74LVC8T245.

Kétirányú módot úgy valósít meg, hogy a DIR lába segítségével az adat irány megfordítható, kimenete push-pull.

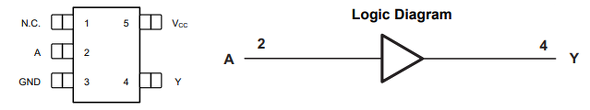

Vannak más megoldások is, amik célspecifikusan 1-1 adatvonal illesztésére szolgálnak, ilyen például a következő is. SN74LV1T34 cél puffer Legfőképpen az LVCMOS (low-voltage CMOS) technológia hívta életre.

A sor az integrált megoldásokkal szinte a végtelenségig folytatható, számos level translator IC létezik már, csak a pénztárca szab határt ezeknek. Pár példa: - TXB0108PWR (8-bites, automatikus kétirányú illesztő) - SN74LVC8T245PW (8-bites, irányváltással rendelkező) - SN74LVC1T45 / 74LVC1T45 (1-bites, hasonló irányváltással rendelkező, Hp41C fórumtárs ajánlása) - CD74AC623 (automatikus kétirányú üzemmóddal is rendelkező 8-bites tri-state szintillesztő, Sick-Bastard fórumtárs ajánlása) Letölthető mellékletek

Értékeléshez bejelentkezés szükséges! |

Bejelentkezés

Hirdetés |